Variegated BIST test approach

A test method and test pattern technology, applied in the direction of digital circuit test, electronic circuit test, measurement of electricity, etc., can solve the problems of large area and increase of test time, and achieve the effect of increasing test depth, increasing test ability and reducing dependence.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

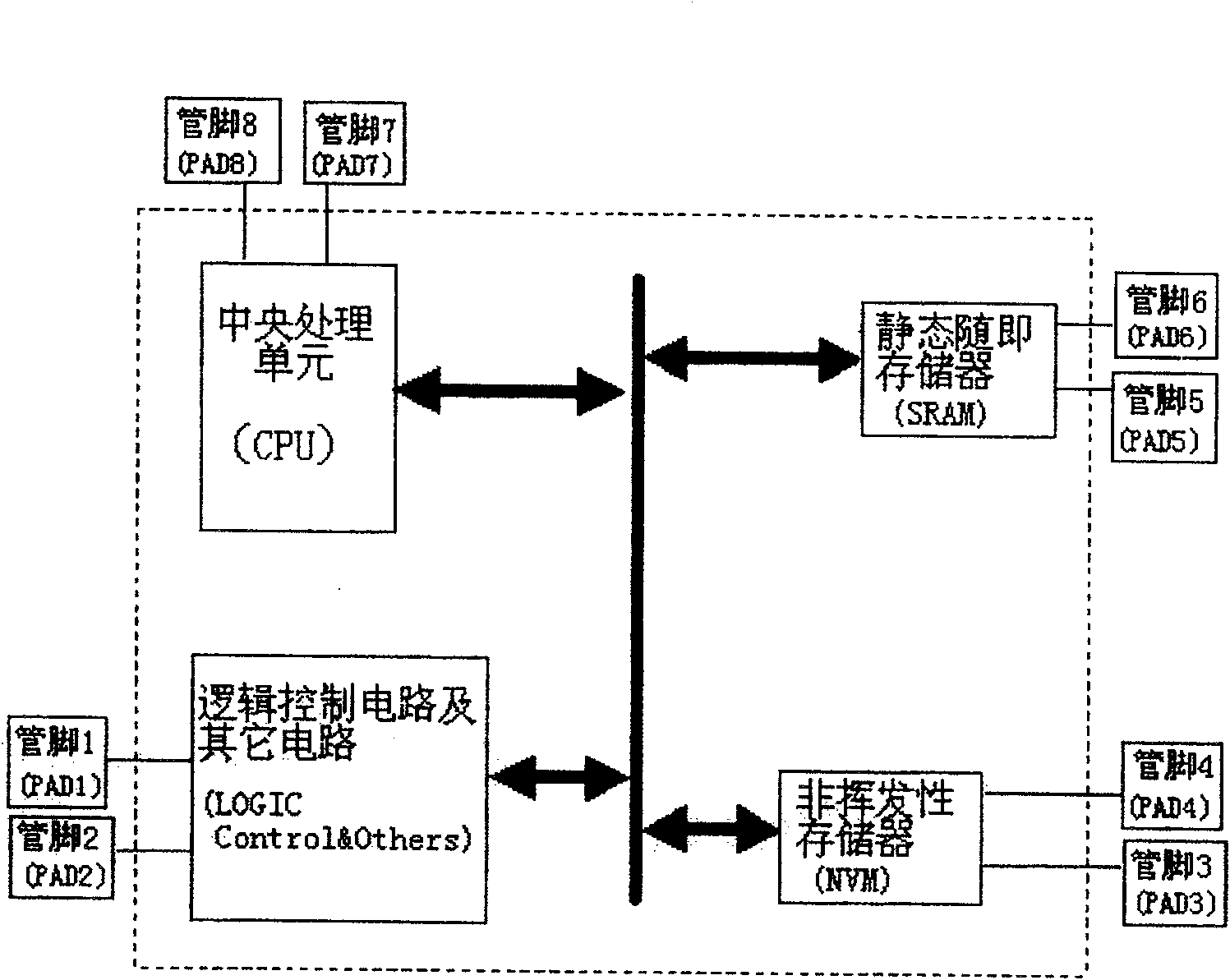

[0019] The BIST test method of the present invention utilizes some resources of the chip itself, especially the rewritable memory resources, to test other part functions of the chip, so as to reduce the impact on the test platform and the chip itself on the basis of ensuring the test error coverage rate. design requirements.

[0020] The embedded Flash area of the chip is usually used to store software codes in actual product applications, and is used for the instruction library for its CPU to operate the system. Use this feature to store all the functional instructions to be tested in the NVM (Non-Volatile Memory, non-volatile memory) area in advance, and then activate the CPU through simple external instructions to call and operate these instructions in the storage area. .

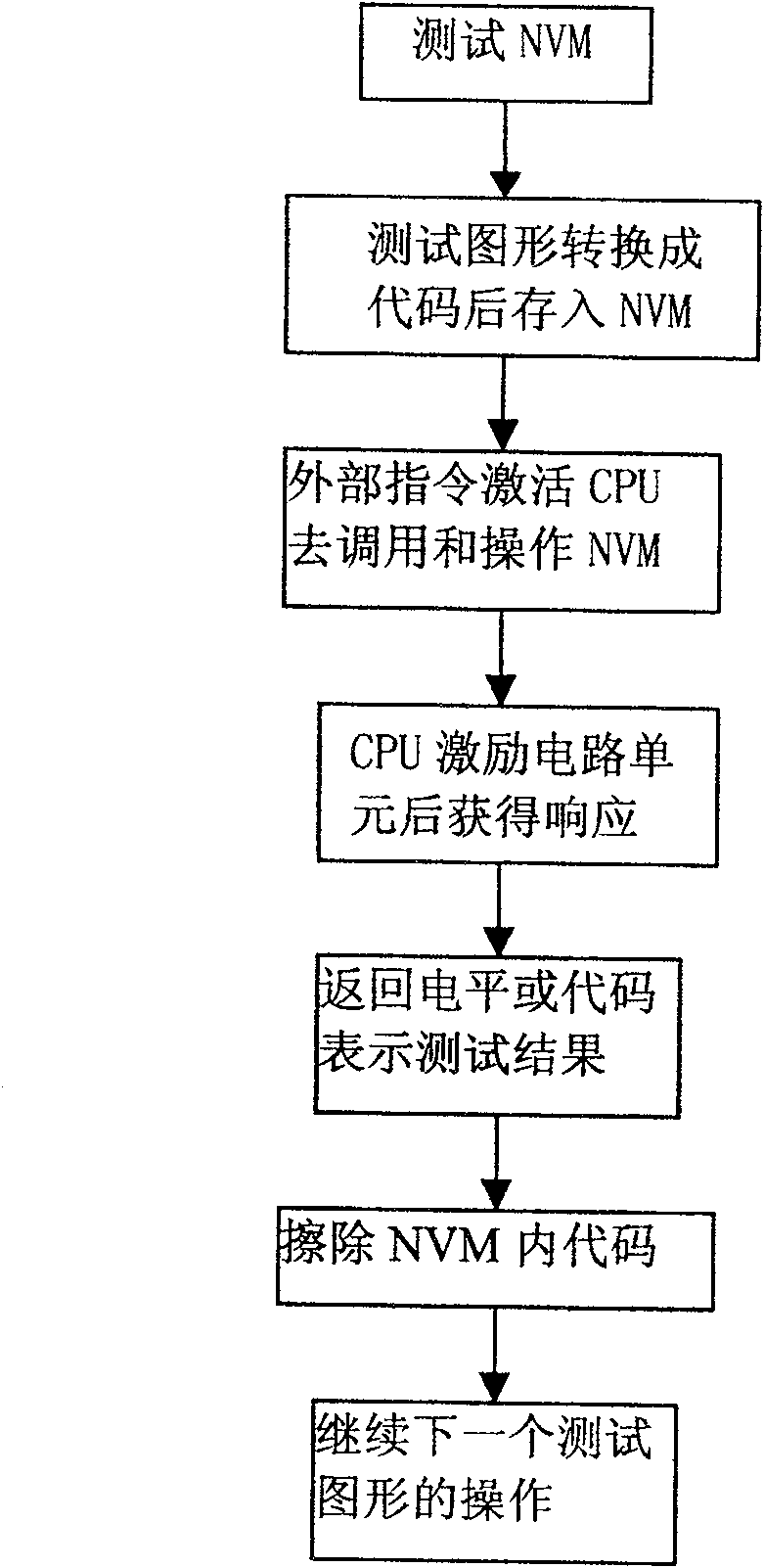

[0021] The BIST test method of the present invention comprises reducing the number of pins, and also includes the following steps (see figure 2 ):

[0022] (1) Test the NVM through the logical inte...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap