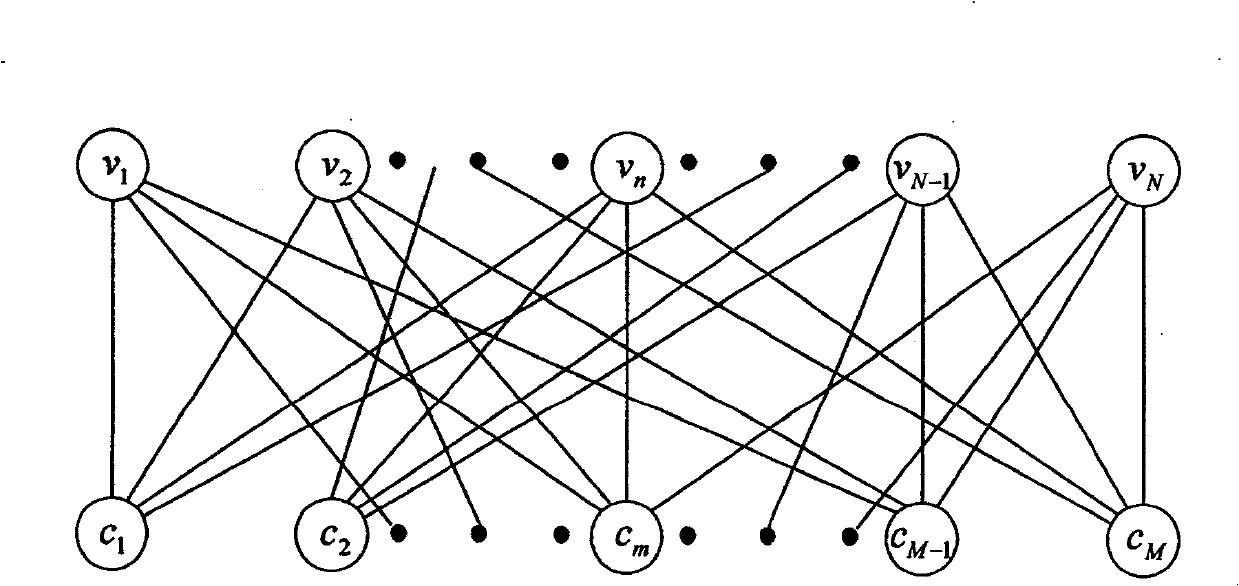

Parallel weighting bit upturn decoding method of low density check code

A technology of weighted bit flipping and low-density parity, which is applied in the decoding field of channel error correction coding, can solve problems such as slow decoding convergence, achieve the effect of reducing computational complexity and improving decoding convergence speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

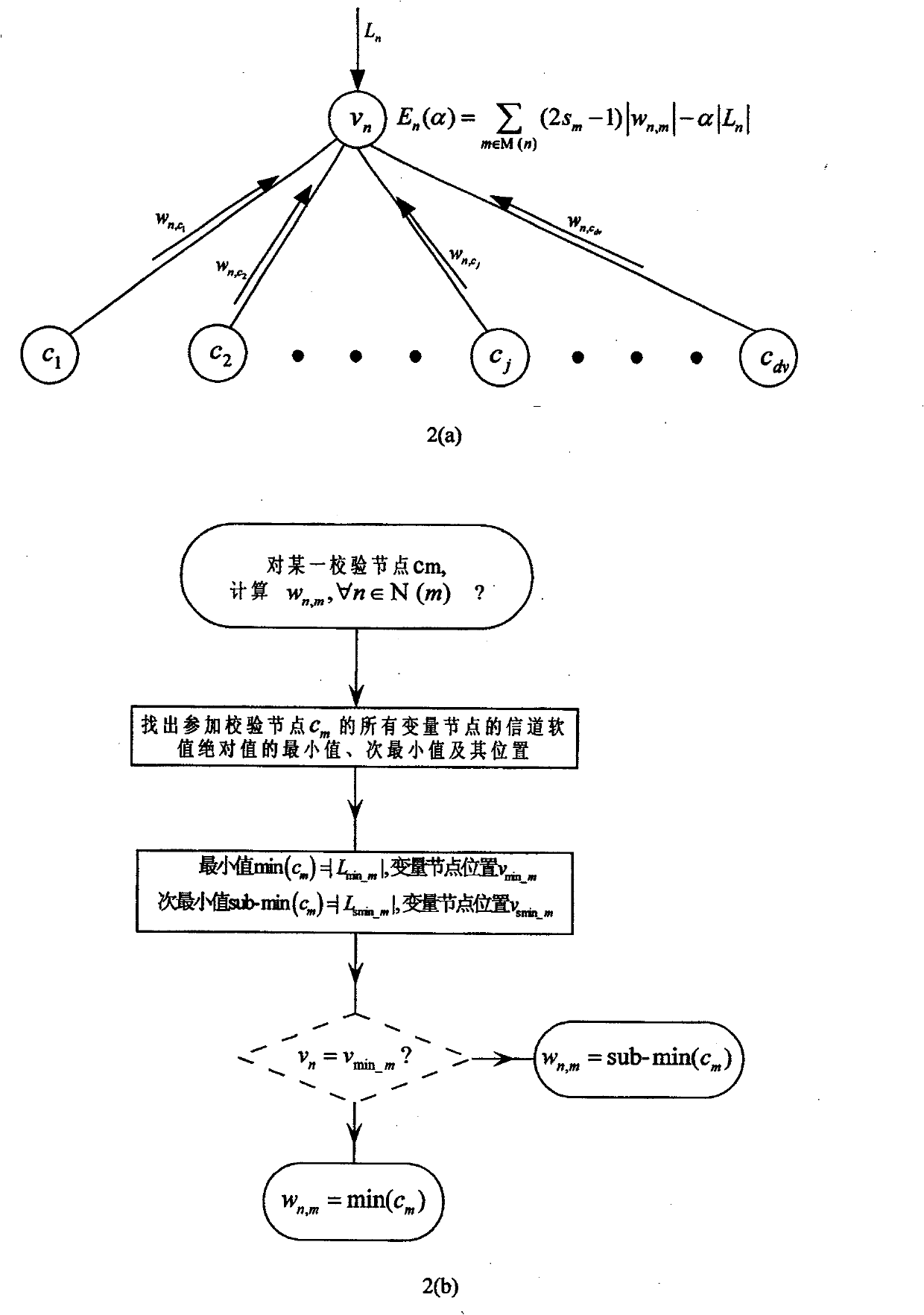

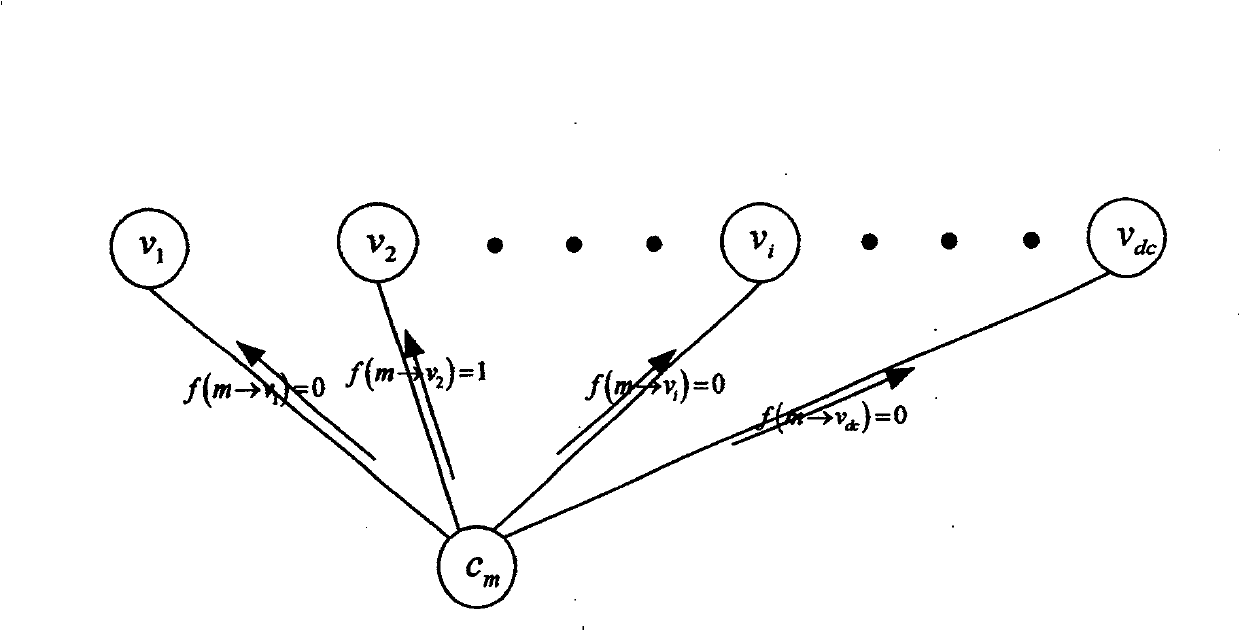

[0048] The parallel weighted bit-flip decoding method of the low-density parity check code of the present invention first performs hard judgment on the channel received information to obtain a hard judgment code word, and then checks whether the judgment sequence satisfies all the verification relations of the check nodes, and if so, decodes Stop; otherwise, for any invalid verification node, find out the variable node with the largest weighted flipping criterion among all the variable nodes participating in the verification, and send a unique flipping unit signal to the variable node; then, each variable node Accumulate the semaphore of the flipping unit, and select all variable nodes whose accumulated semaphore is greater than the given flipping threshold, perform parallel bit flipping on the corresponding position of the hard-judgment codeword, and update the hard-judgment codeword at the same time, and the algorithm enters the next iteration.

[0049] The specific steps are...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com