Method and system for testing chip

A chip to be tested, chip technology, applied in the field of testing, can solve problems such as difficult comparison

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

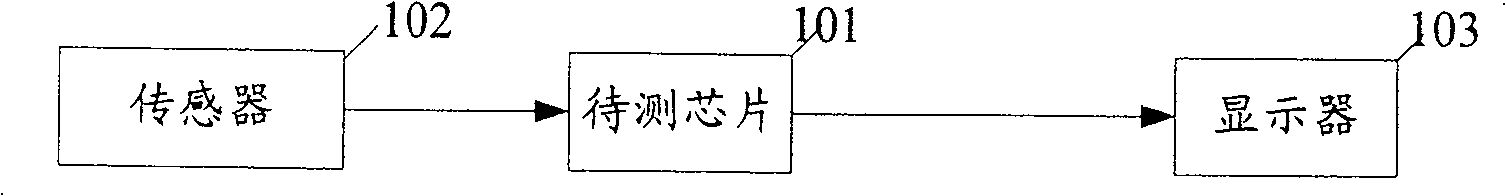

[0051] Firstly, the general inventive idea of a chip testing system of the present invention is introduced.

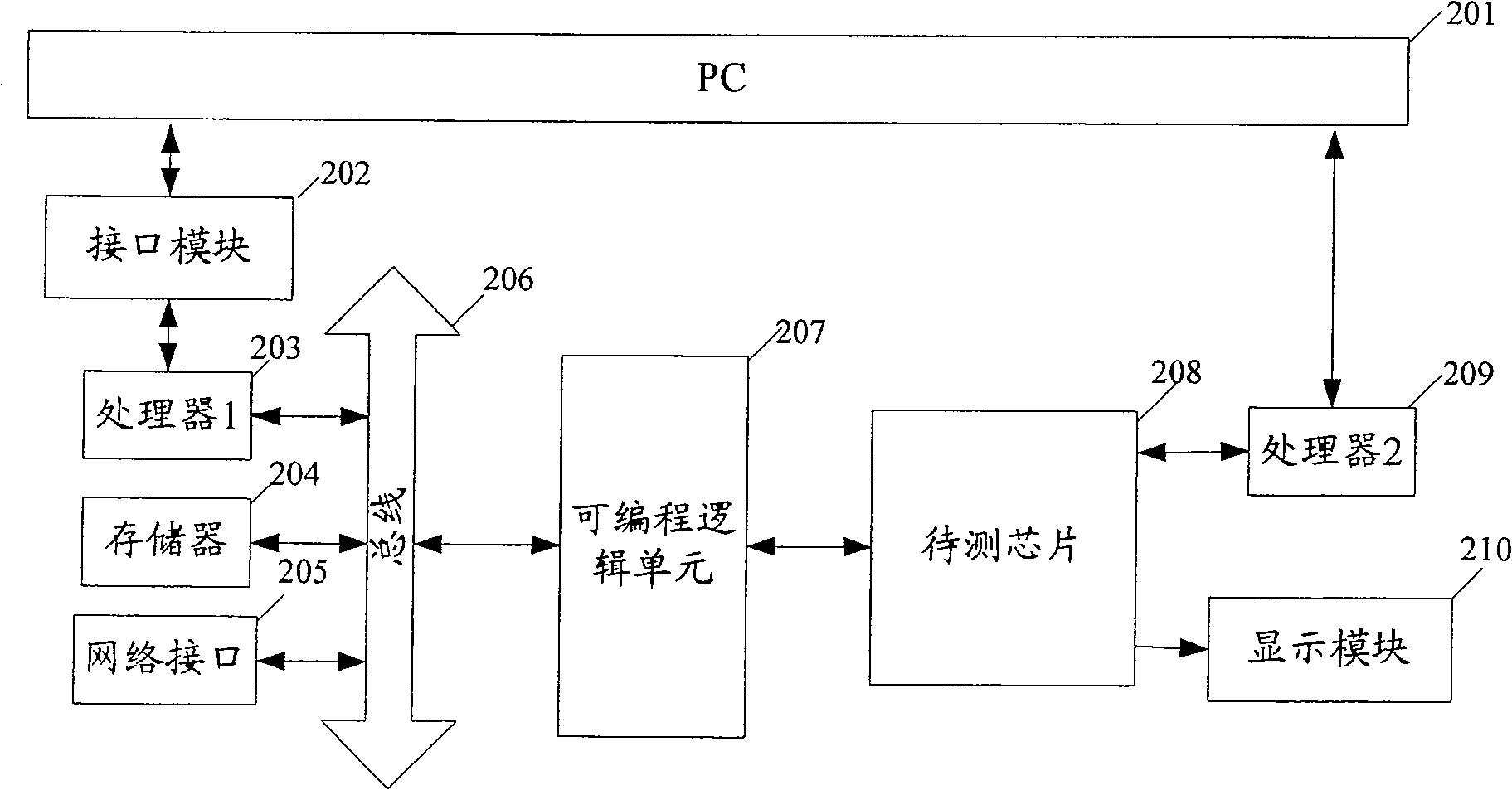

[0052] like figure 2 As shown, a system of a test chip of the present invention includes a PC 201, an interface module 202, a processor 1203, a memory 204, a network interface 205, a bus 206, a programmable logic unit 207, a chip to be tested 208, a processor 2 209 and a display Module 210.

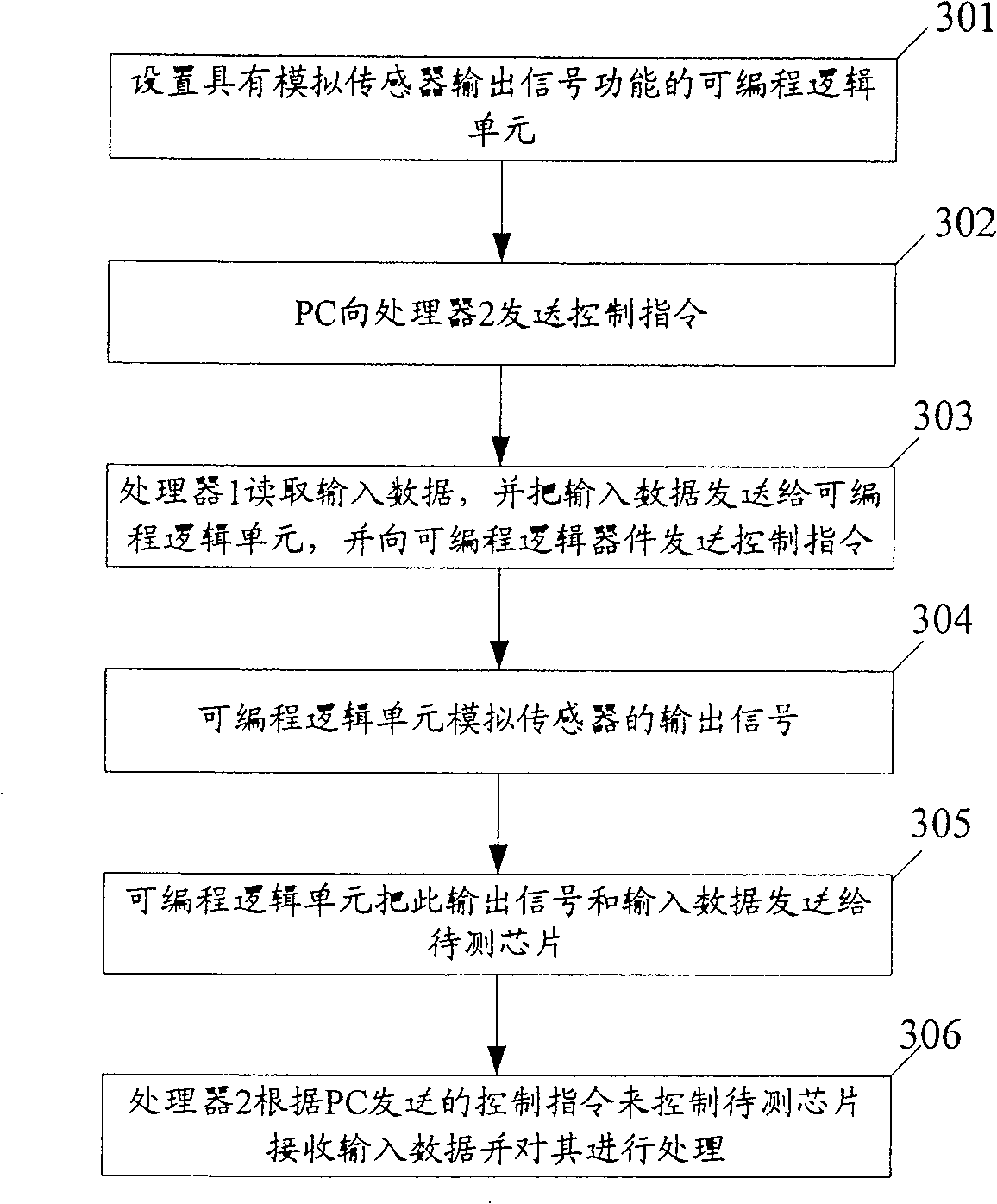

[0053] PC201 sends a control instruction to processor 1203 through interface module 202, processor 1203 reads the input data on the memory 204 through bus 206 according to the control instruction, and processor 1203 sends the input data to programmable logic unit through bus 206 207, and send a control instruction to the programmable logic unit 207, the programmable logic unit 207 simulates the output signal of the sensor according to the control instruction, and sends the output signal and input data to the chip 208 under test. PC201 sends a control instruction to processor ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com