Method for forming silicon trench

a technology of silicon trenches and ladi, applied in the field of silicon trenches, can solve the problems of limited ladi line width and depth, and high cost, and achieve the effect of low cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example

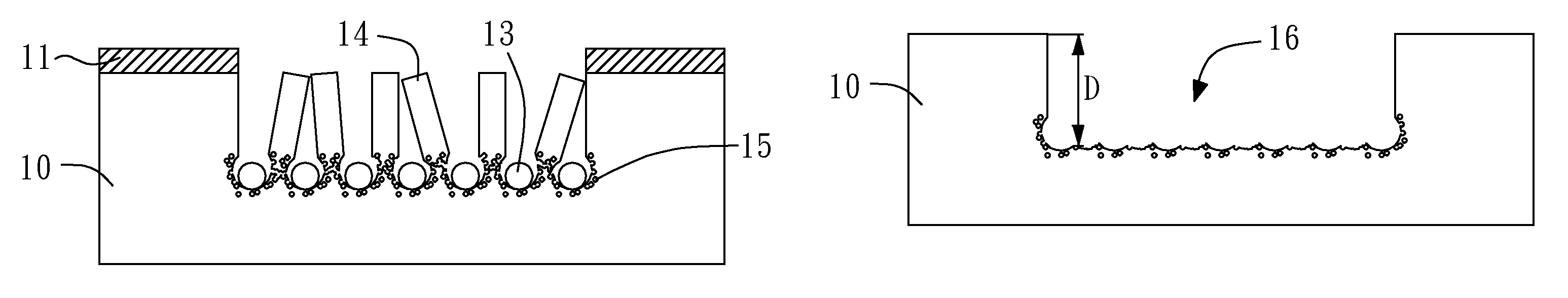

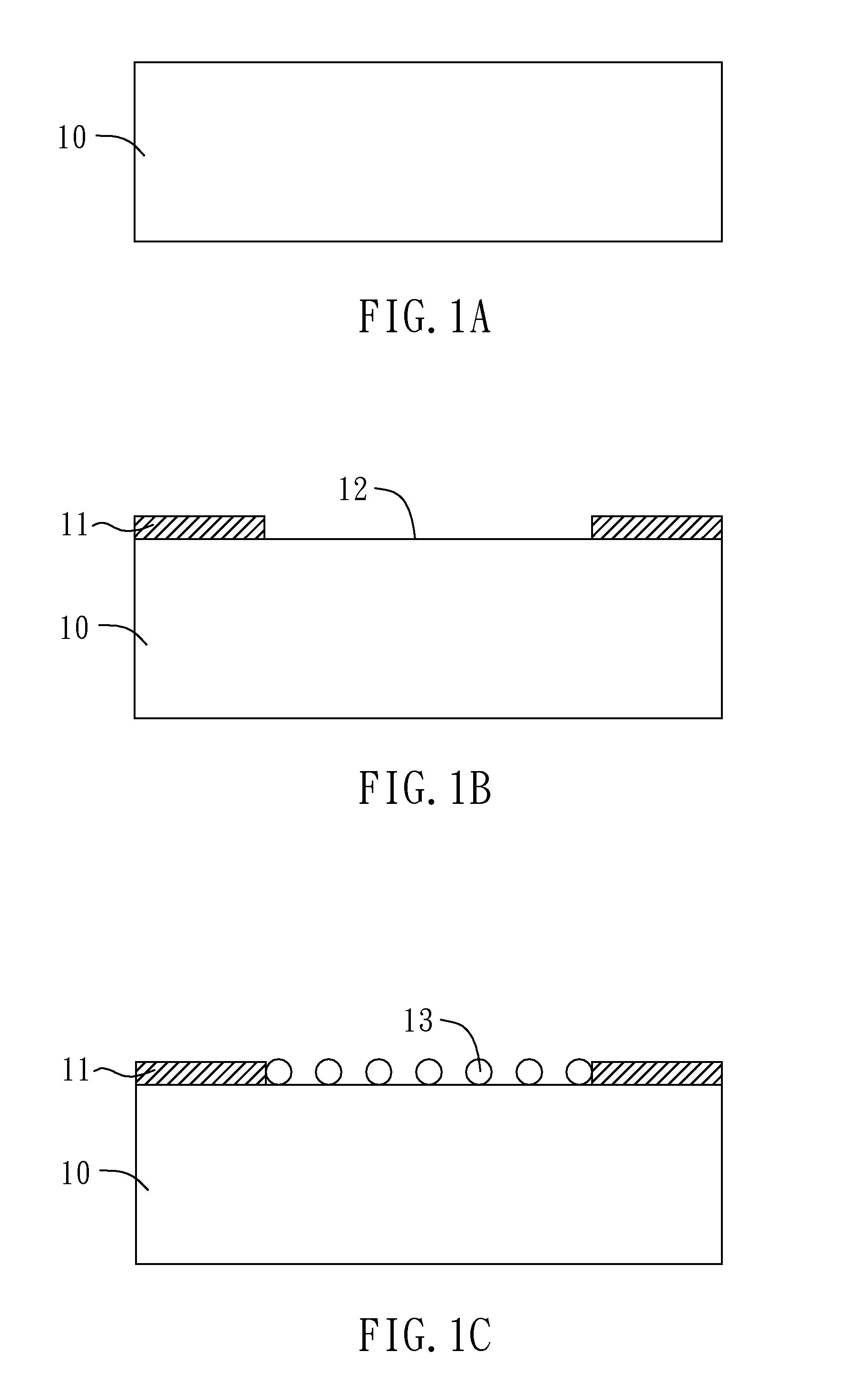

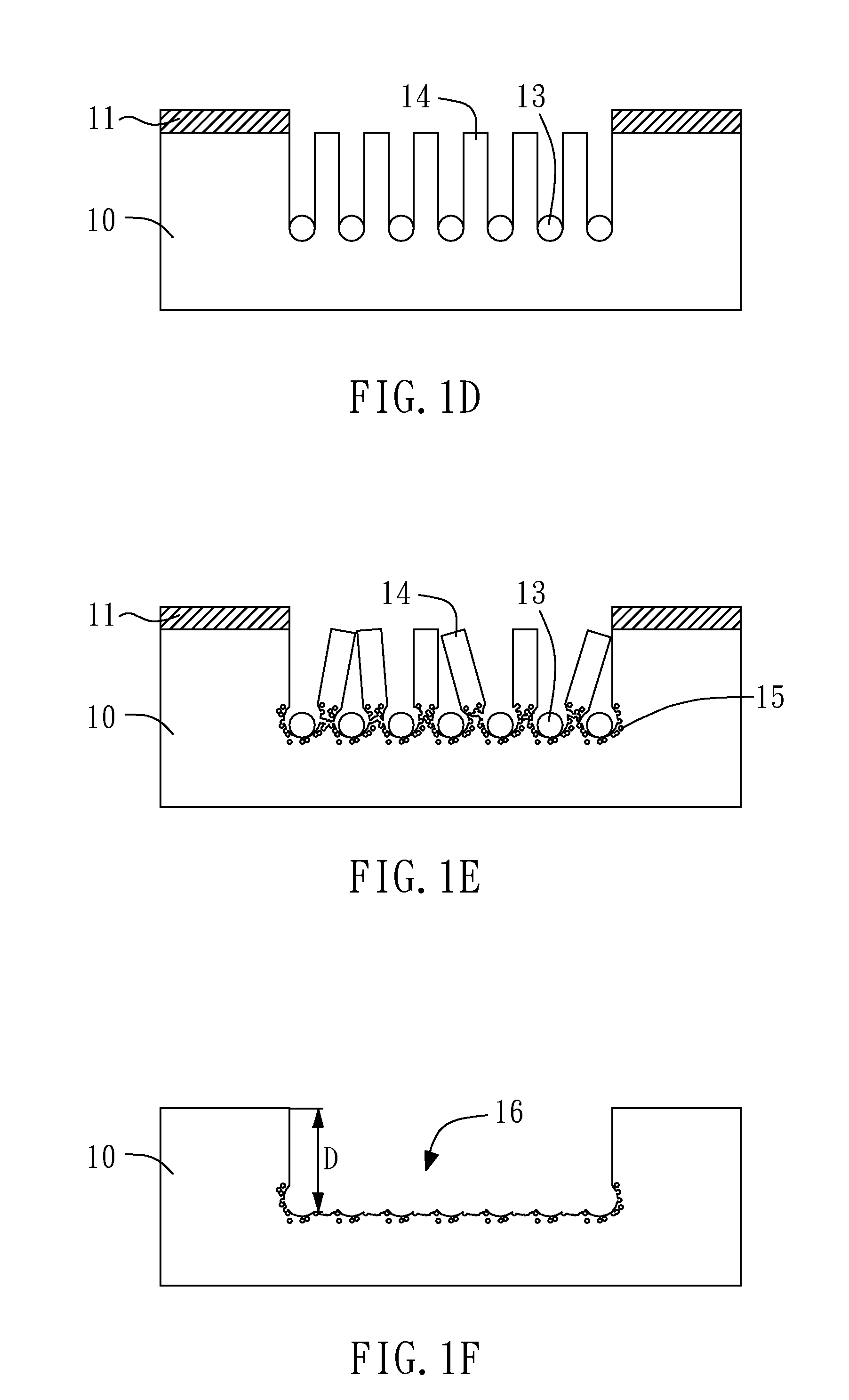

[0027]This example employs silver as the center of the redox reaction, illustrating how silicon trenches are formed. First, a p-type Si wafer with a resistance of 1-10 Ωcm is provided and cleaned. Then, the Si wafer is spin coated with a photoresist (positive photoresist S1813) and the photoresist is patterned to define etching areas by using a typical photolithography process. Then, the Ag catalysts were subsequently deposited on the etching areas through EMD method. For example, the Si wafer is immersed in an aqueous HF / AgNO3 solution including 0.02 mol / L AgNO3 and 10 vol. % HF in deionized water about 20 sec, so as to deposit Ag catalysts on the etching areas.

[0028]Then, the silicon wafer is immersed in the above HF / AgNO3 solution again for 10 to 30 min. Alternatively, the silicon wafer is immersed in an aqueous HF / H2O2 solution including 0.6 vol. % H2O2 and 10 vol. % HF in deionized water for about 10 to 30 min. The Ag ions of the solution will be selectively deposited on the Ag...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com