Single datapath floating point implementation of RCP, SQRT, EXP and LOG functions and a low latency RCP based on the same techniques

a floating point, single datapath technology, applied in the field of computer systems, can solve problems such as large gate counts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

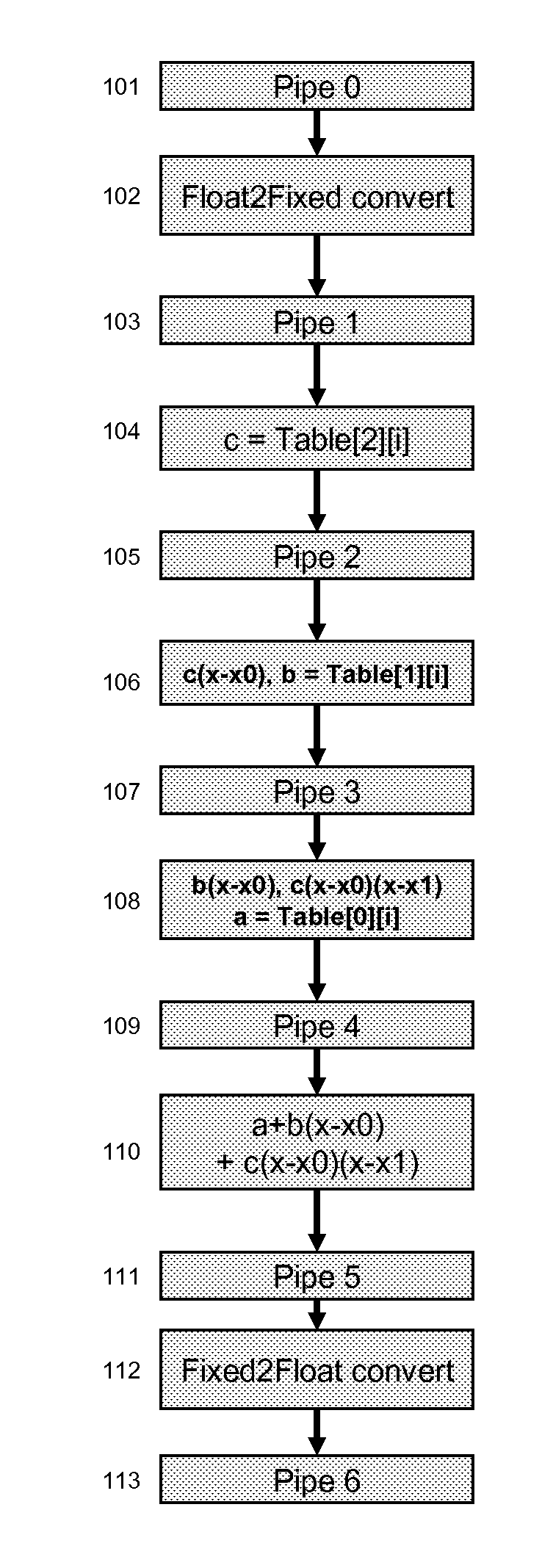

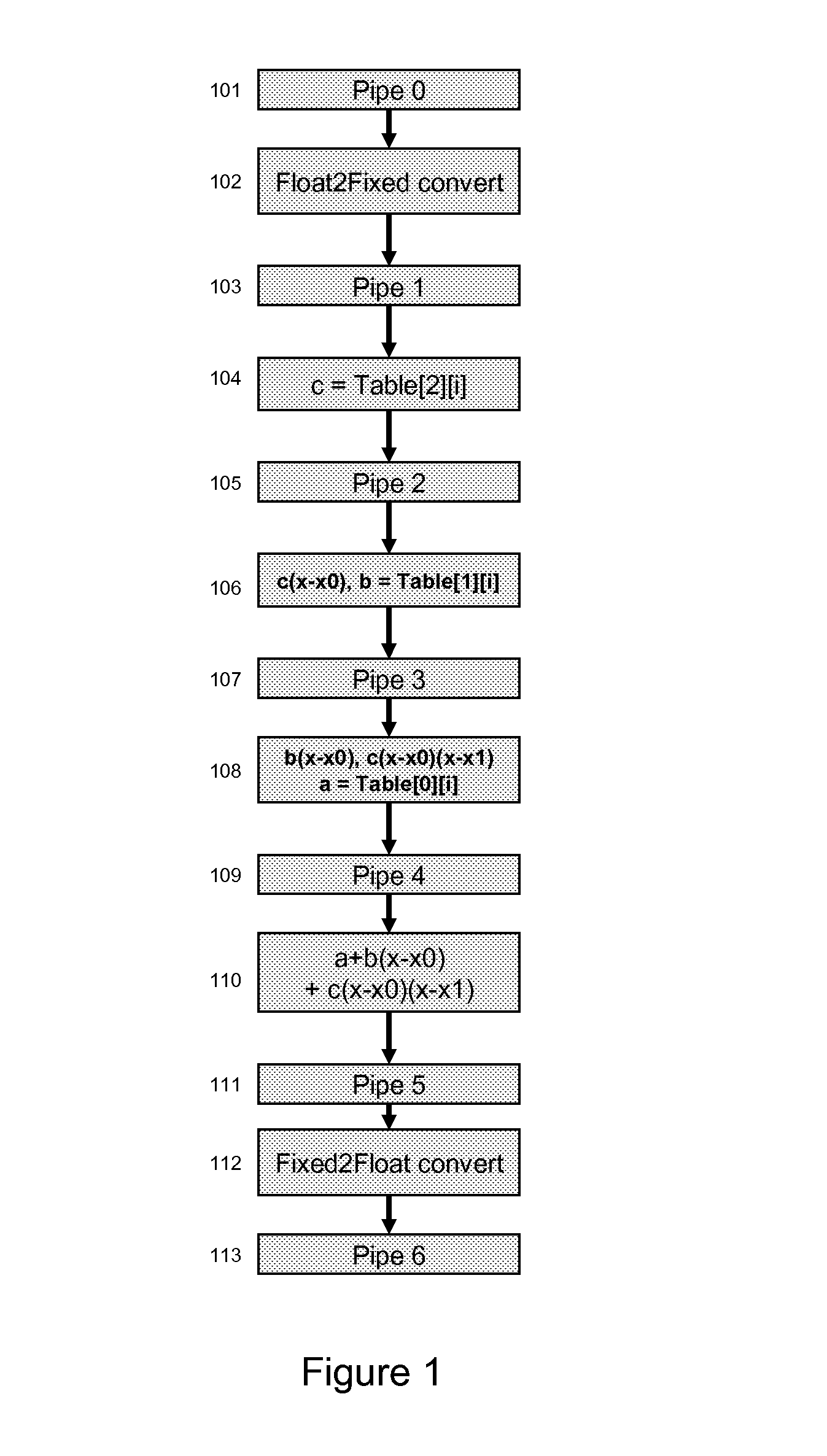

[0022]FIG. 1 is a block diagram illustrating a 6 stage unified hardware pipeline according to an embodiment of the present invention. Here, block 101, block 103, block 105, block 107, block 109, block 111, and block 113 are the register stages of the pipeline. Block 102 is a floating point to fixed point converter. Block 112 is a fixed point to floating point converter. In an example, block 112 may be configured to be bypassing circuit according to an opcode (i.e., a configuration instruction, a micro-code, or the like) for implementing an EXP function. In another example block 102 may be configured to be bypassing circuit according to another opcode (i.e., a configuration instruction, a micro-code, or the like) for implementing an LOG function. In still other examples, both block 102 and block 112 may be configured to be bypassing circuits according to yet another opcode (i.e., a configuration instruction, a micro-code, or the like) in implementing RCP or SQRT functions. In some ex...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com