A power mosfet having laterally three-layered structure formed among element isolation regions

a technology of power mosfet and isolation region, which is applied in the direction of transistors, electrical devices, semiconductor devices, etc., can solve the problems of cost and time, complicated manufacturing process of the mosfet disclosed in document 1 and difficulty in meeting both conditions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

>

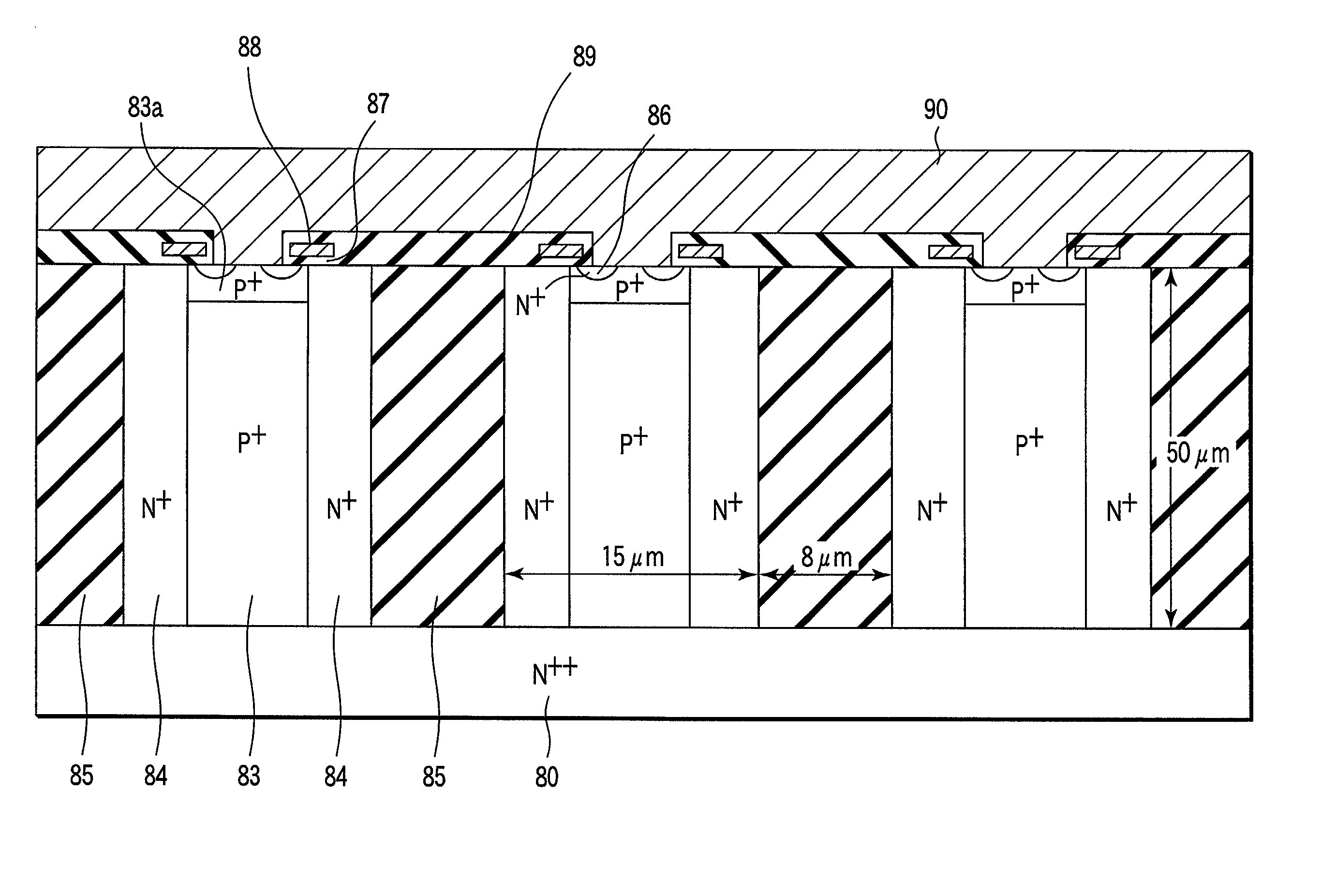

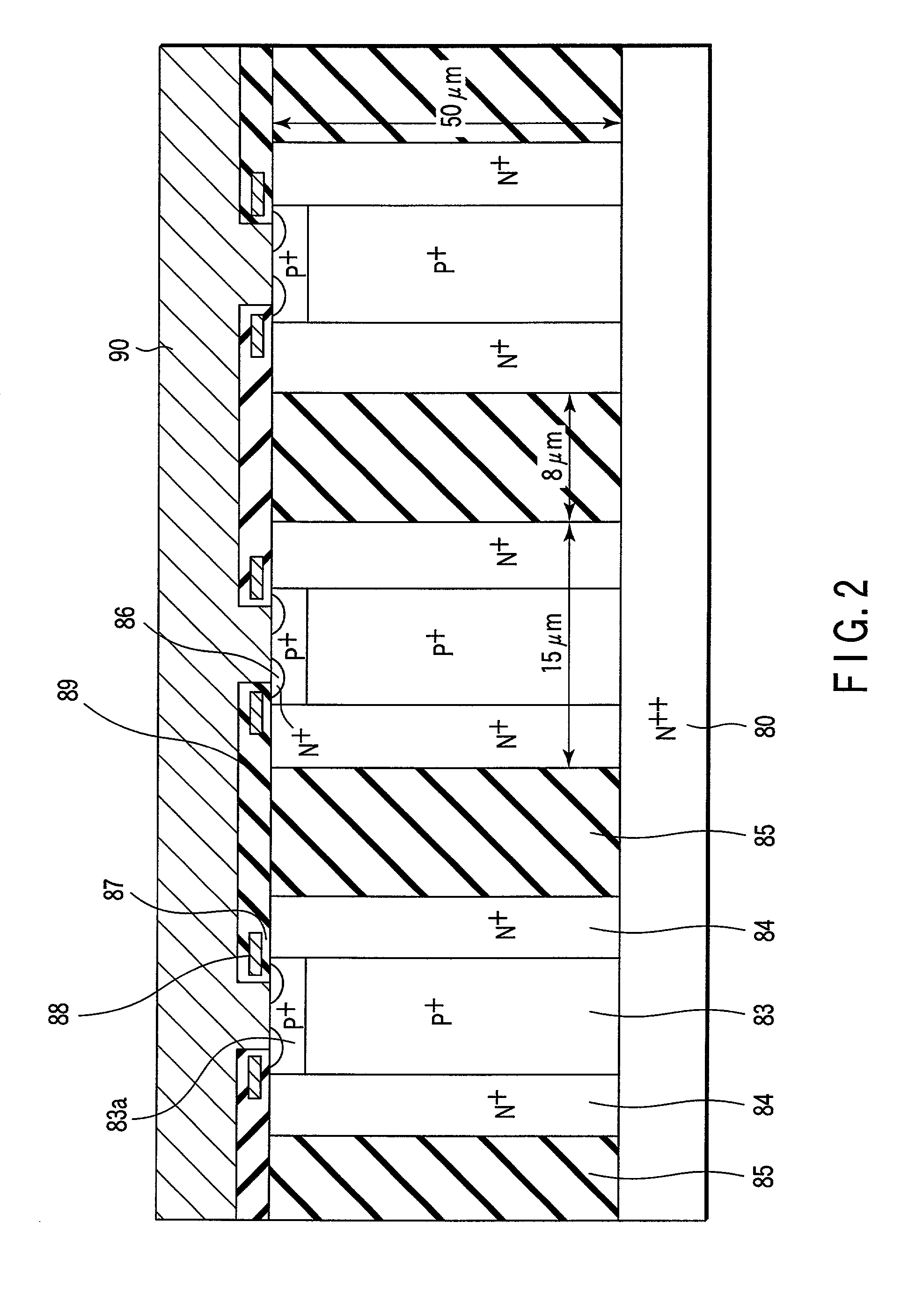

[0123] In the first to third embodiments, as shown in FIG. 5, the N.sup.++ region 84a may be formed in the portion continued to the trench side wall portion in the surface of the N.sup.+ pillar layer 13, so that the depletion layer is prevented from reaching the upper surface of the N.sup.+ pillar layer 13 during applying of the voltage.

[0124] Moreover, for the element isolation region and edge termination isolation region, as shown in FIG. 6, after formation of the dielectric film (e.g., Si.sub.3N.sub.4 or SiO.sub.2) 85a on the trench inner wall, the insulator (poly silicon or SiO.sub.2) 85b may be buried.

[0125] Additionally, in the above description, the N-type DTMOS has been described, but the present invention can similarly be applied to a P-type DTMOS. In this case, a first conductivity type is a p-type, a second conductivity type is an n-type, and the P.sup.+ pillar layer in a PNP pillar layer constitutes the current path between the P.sup.+ source region and the drain.

[0126]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com