Impedance calibrating circuit

A technology for calibrating circuits and impedance matching circuits, applied in logic circuits, line impedance variation compensation, input/output impedance improvement, etc., and can solve problems such as signal reflection noise aggravation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

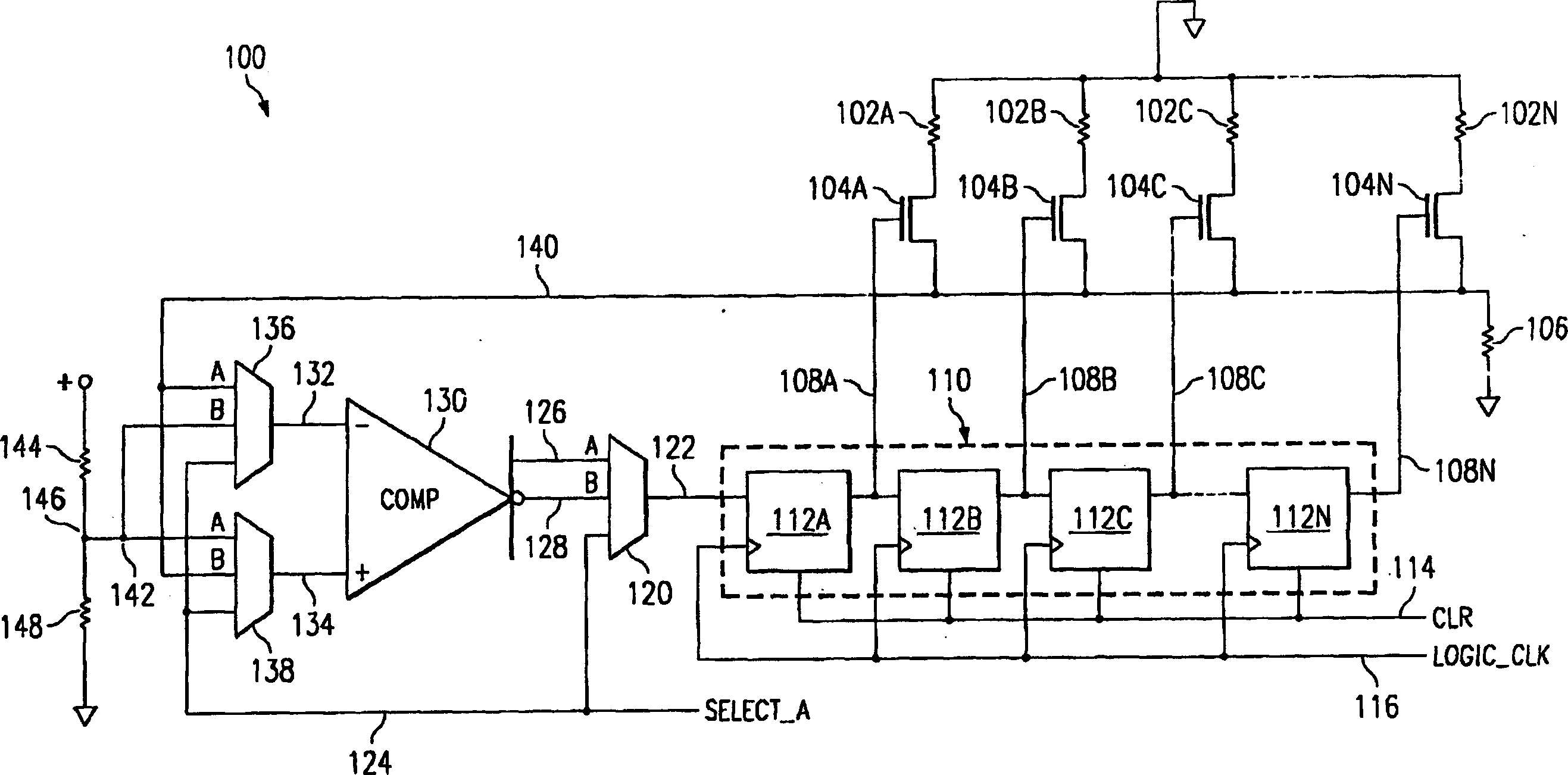

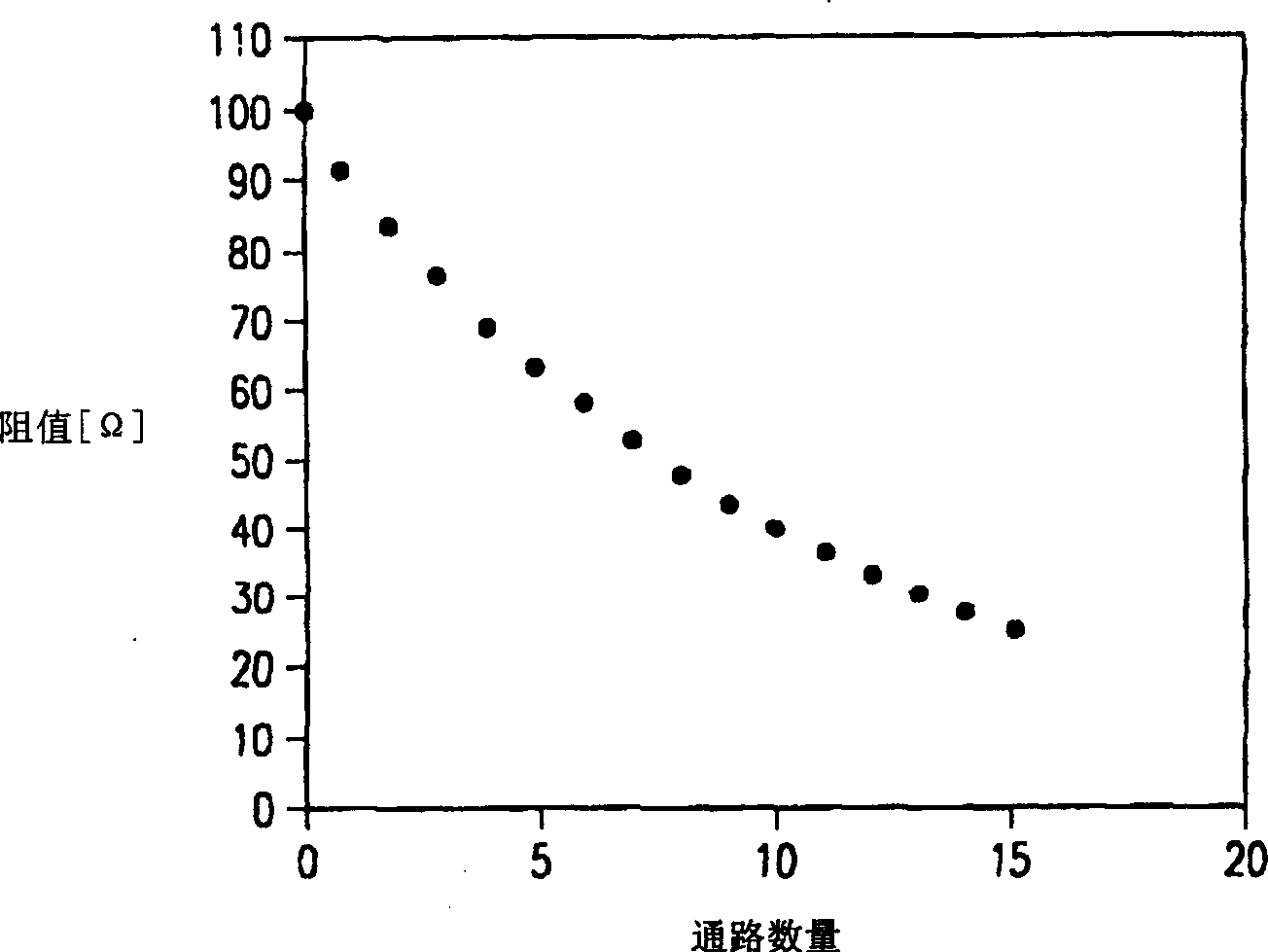

[0018] figure 1 The circuit shown implements the impedance calibration technique of the present invention. Impedance calibration is provided by a plurality of parallel resistors 102A, 102B, 102C...102N, where N is an integer. Each resistor is selected by a corresponding transistor 104A, 104B, 104C...104N. The common end of the resistors is connected to a voltage source and the select end of the resistors is connected to a resistor 106, the other lead of which is connected to ground. Each resistor 104A, 104B, 104C...104N acts as a switch controlled by a signal on line 108A, 108B, 108C...108N respectively. These signals are the outputs of the shift register 110 . Another register arrangement with similar characteristics could also be used. The more transistor 104 is turned on, the less impedance the array becomes.

[0019] Shift register 110 is composed of flip-flops 112A, 112B, 112C . . . 112N, and is connected to flip-flop 112A by serial input 122 . The output of each fl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com