Carbon nano tube NOR logic device

A logic device and carbon nanotube technology, applied in the field of logic devices, can solve the problems of complex device structure and difficult fabrication, and achieve the effects of simple device structure, easy fabrication materials, and easy fabrication and integration.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

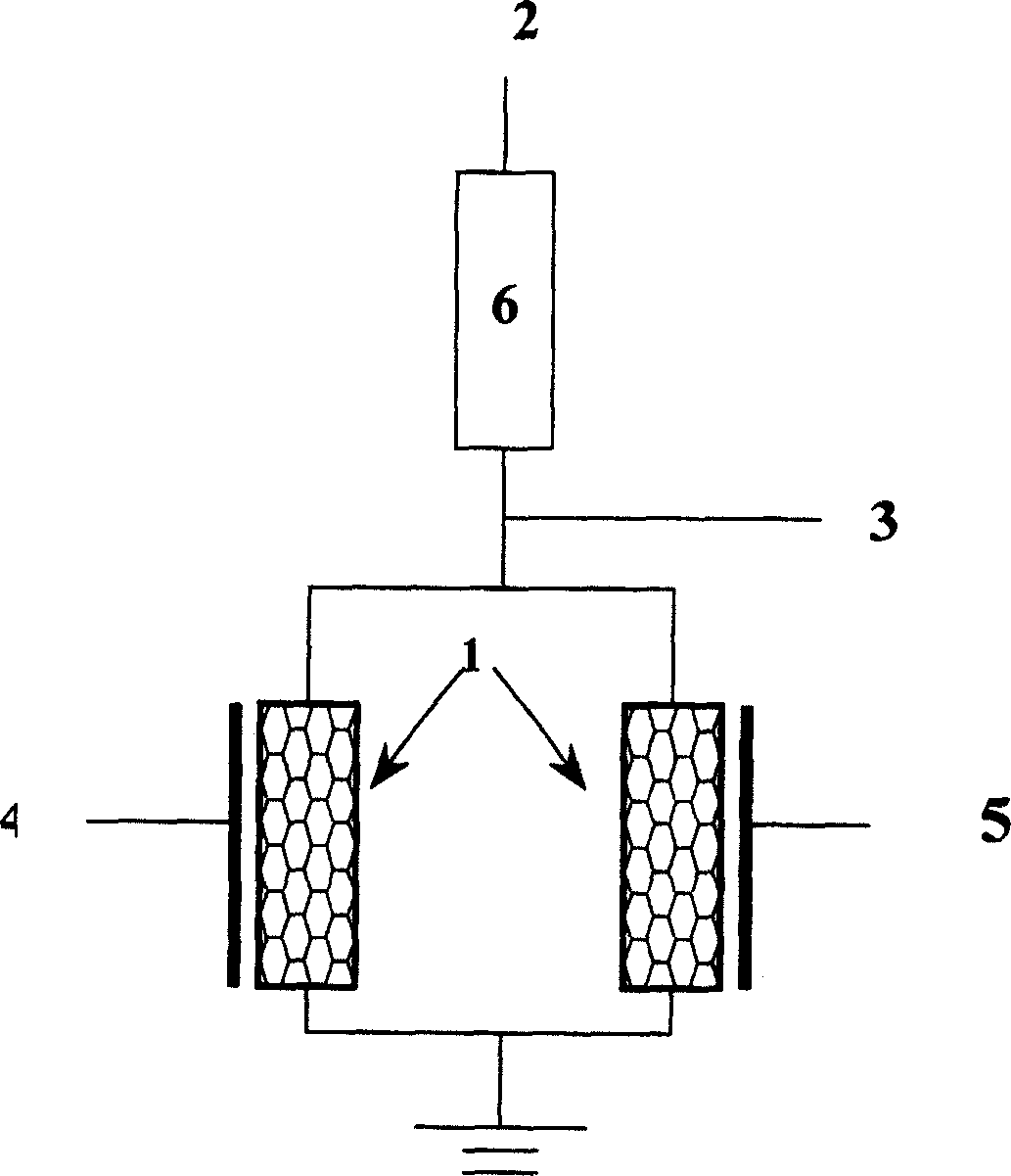

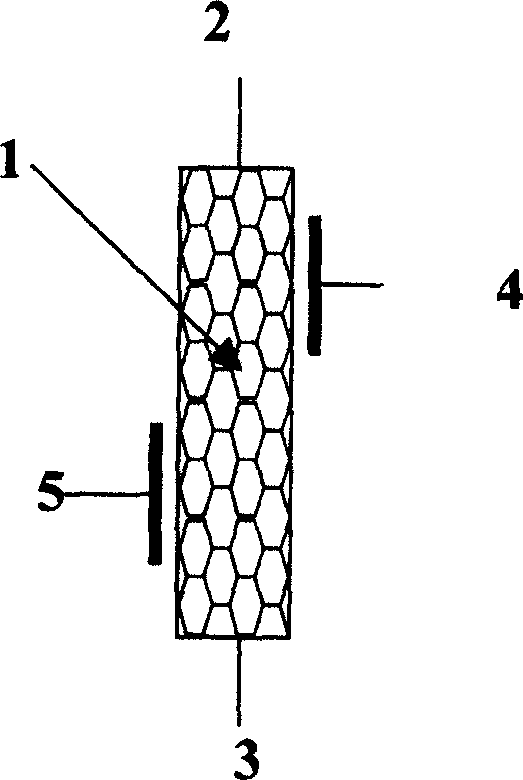

[0027] refer to figure 2 , 3 and 4, the structure of the carbon nanotube "or-no" logic device of the present invention is described in detail in combination with the manufacturing method and the embodiment:

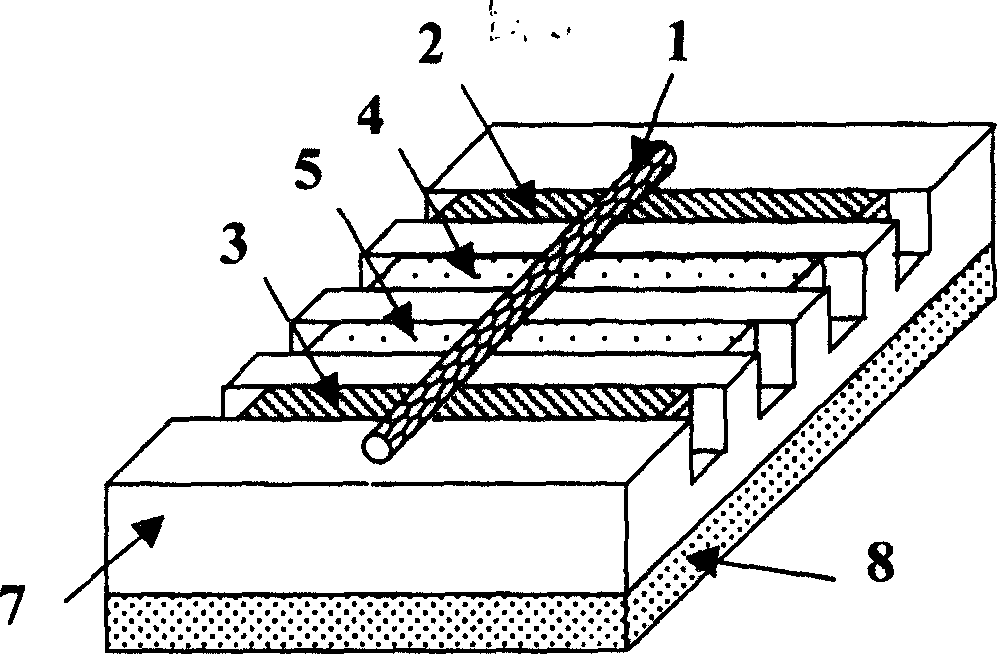

[0028] Silicon with (001) orientation is selected as the substrate 8 . Form 300nm thick SiO by using organic vapor phase deposition method (PECVD) 2 insulating layer7. In SiO 2 Electron photoresist (PMMA) with a thickness of 80 nm is evenly covered on the insulating layer 7 . After the photoresist is exposed, two trenches with a width of 30 nm and a distance of 50 nm are formed on the photoresist. Applying dry etching, the SiO exposed in the photoresist 2 Grooves with a width of 30 nm and a depth of 30 nm are etched on the insulating layer 7 for making gates 4 and 5 . A layer of Al with a thickness of 30nm is deposited on the surface by electron beam evaporation method. After stripping and cleaning, the intrinsic oxidation method is used to form 2-3nm thick Al on...

Embodiment 2

[0049] refer to image 3 , 4 and Figure 5 , the structure of this embodiment is described in detail in conjunction with the manufacturing method:

[0050] Silicon with (001) orientation is selected as the substrate 8 . Form 300nm thick SiO by using organic vapor deposition method (PECVD) 2 insulating layer7. In SiO 2 Electron photoresist (PMMA) with a thickness of 80nm is evenly covered on the insulating layer 7; after the photoresist is exposed, two grooves with a width of 30nm and a distance of 50nm are formed on the photoresist. Using dry etching, the photoresist exposed SiO 2 A groove with a width of 30 nm and a depth of 30 nm is etched on the insulating layer 7 . A layer of Al with a thickness of 30nm is deposited on the surface by electron beam evaporation method. After stripping and cleaning, the intrinsic oxidation method is used to form 2-3nm thick Al on the Al surface. 2 o 3 Insulation. In this way, the preparation of the first grid 4 and the second grid ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com