Treating method and system for local defect internal memory

A processing method and a processing system technology, which are applied in the processing and system field of local defect memory, and can solve the problem that CPU1 cannot recognize the instruction part, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

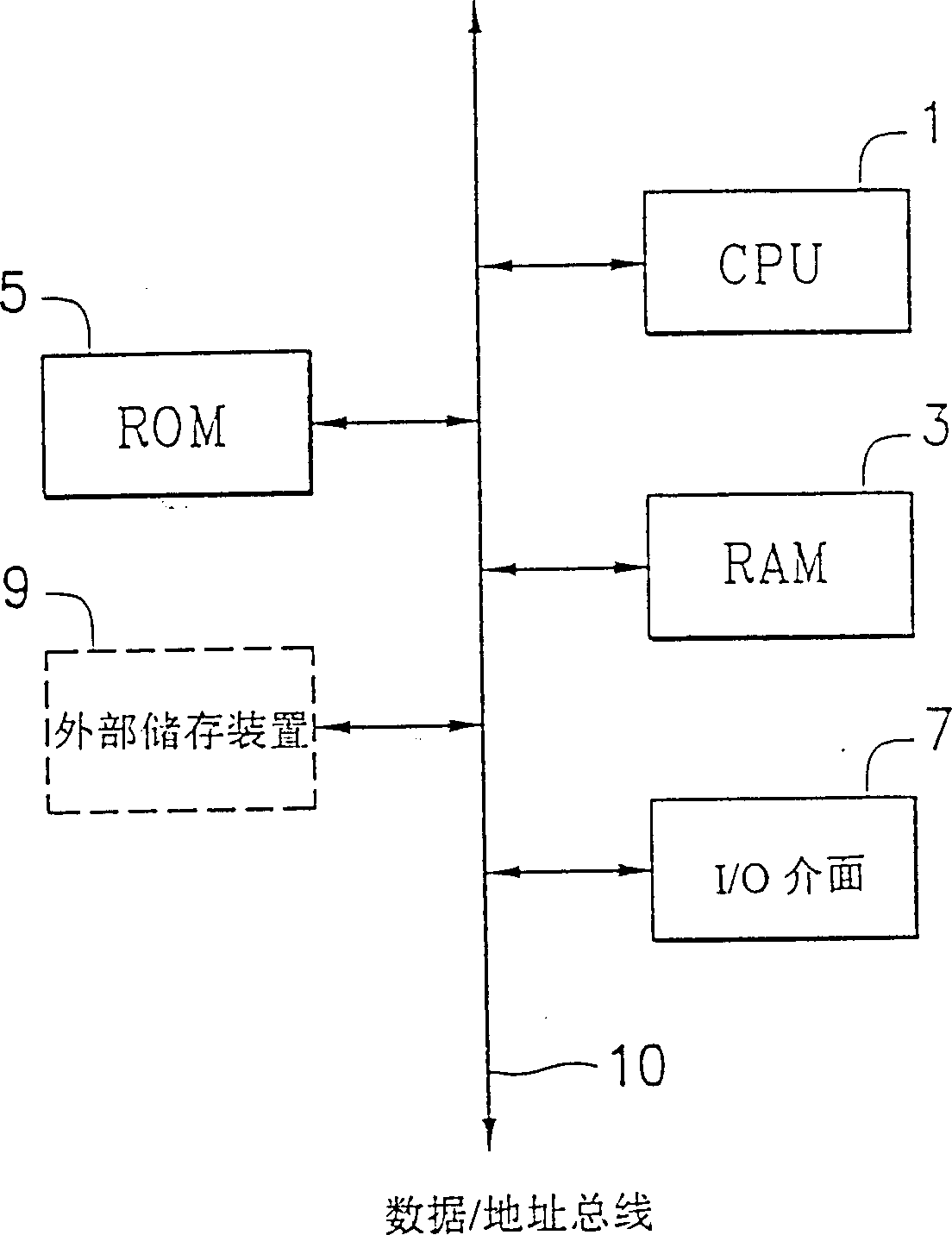

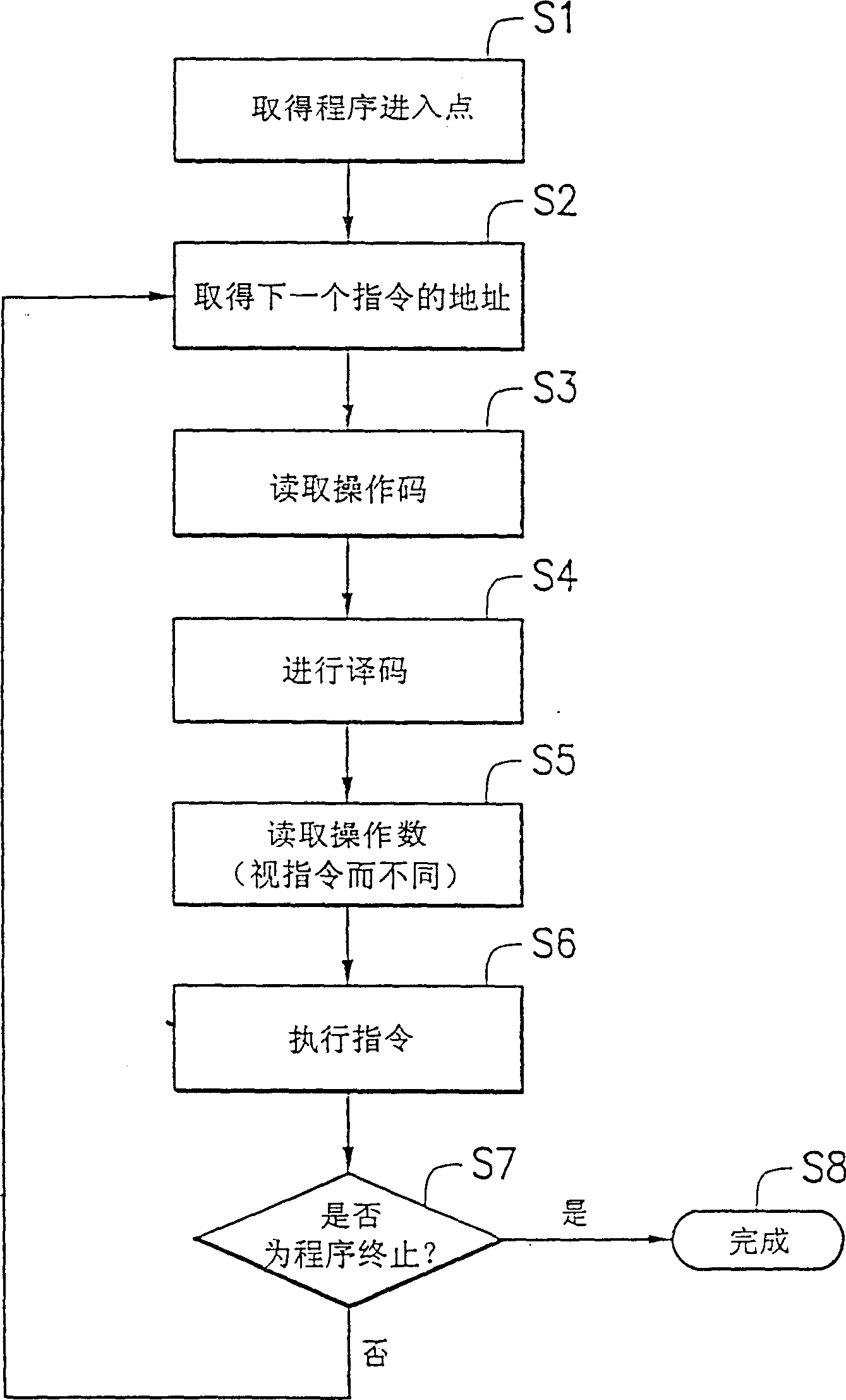

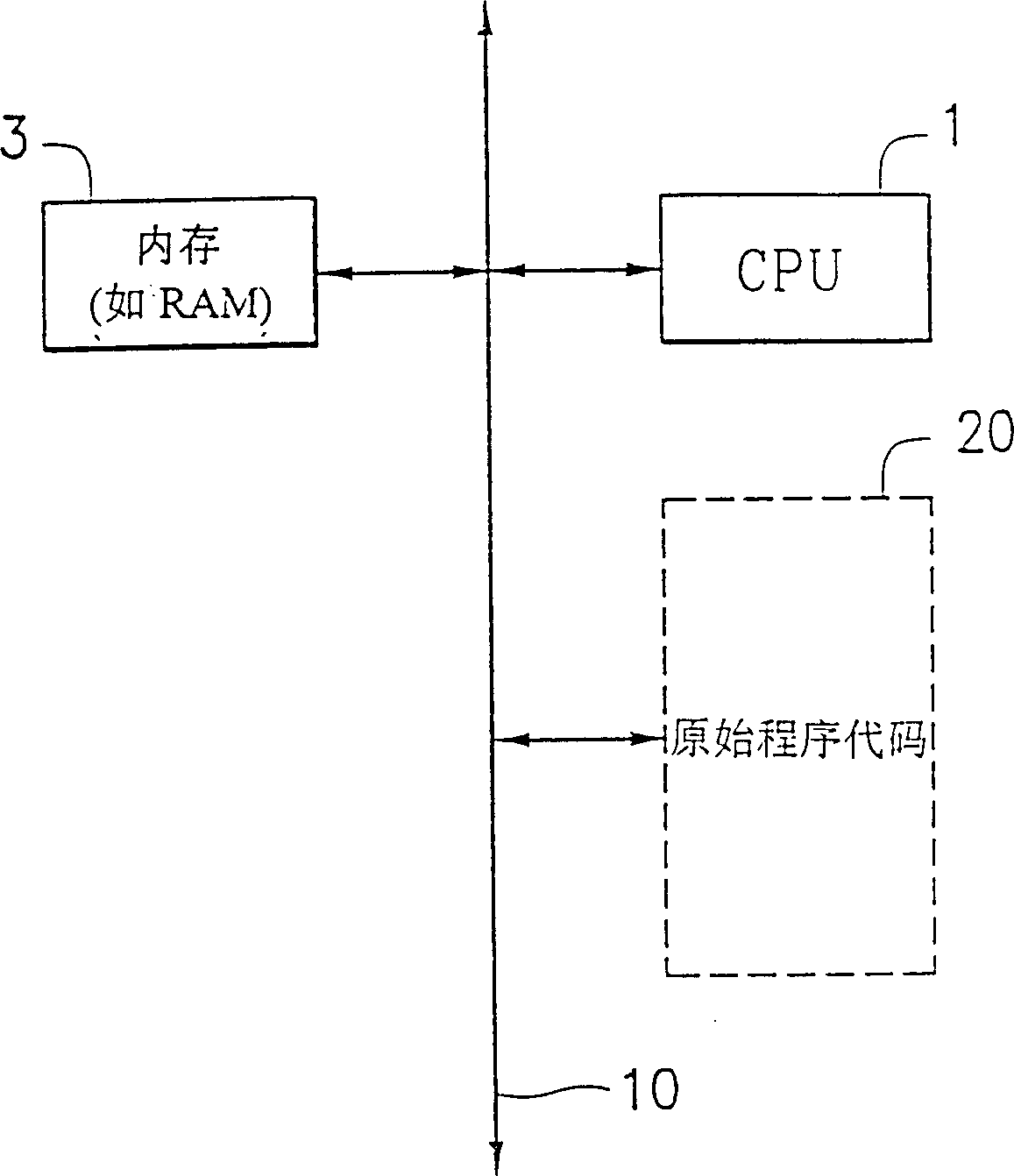

[0071] Fig. 3 shows a configuration diagram of the local defect memory processing system of the first embodiment. In FIG. 3 , the memory 3 includes at least one defective storage unit. In the following descriptions, unless otherwise specified, a single defective storage unit or a group of adjacent defective storage units is used as a preset condition. The CPU 1 is preparing to load the original program code 20 into the memory 3 through the data / address bus 10 , and the storage units to be loaded by the original program code 20 include the defective storage units mentioned above. Therefore, the loader (loader) executed in CPU1 must perform some pre-processing actions to ensure that the loaded original program code 20 will not occupy the defective storage unit, and the original program code 20 itself can still be normal. implement. In this embodiment, CPU1 and memory 3 can coexist in the same integrated circuit, such as the application of a single chip system (system on a chip)...

no. 2 example

[0089] Although the processing method of a certain program has been disclosed in the first embodiment, which can solve the problem of partially defective memory, there are still some programs that can be changed. For example, this embodiment is produced by changing the scanning processing method of the original program code and the order of loading the memory from the first embodiment.

[0090] FIG. 9 shows a flow chart of the local defect memory processing method of the second embodiment. As shown in Figure 9, on the one hand, CPU1 determines the physical location of the defective storage unit (S20) and determines the corresponding defect address (S21) of the defective storage unit in the original program code 20; 20 performs scanning (S22). The defect address of the defective storage unit can be determined by step S20 and step S21, and the divisible break point in the original program code 20 can be determined by step S22. This synchronization processing can be applied to ...

no. 3 example

[0094] The first and second embodiments are applicable to the situation that the original program code has not been loaded into the internal memory. At this time, the CPU (microprocessor) can perform pre-processing before the original program code is loaded into the internal memory, so as to adjust the program code to Avoid defective memory cells. However, the situation to be dealt with in this embodiment is the phenomenon that the original program code has been successfully loaded into the memory, but some storage units show weakened functions after a period of time. These degraded memory cells can be read normally at present, but after a certain period of time, the logic value read from them will become increasingly illegible. At this time, the original program code content in the memory must be adjusted to avoid these defective storage units with weakened functions.

[0095] Fig. 10 shows a configuration diagram of a local defect memory processing system of the third embodim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com