Chip packaging method, chip packaging body and electronic device

A chip packaging and electronic device technology, applied in circuits, electrical components, semiconductor devices, etc., can solve problems such as low bottom pad strength, structural reliability defects, and product welding pads falling off.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The technical solutions in the embodiments of the present application will be clearly and completely described below with reference to the drawings in the embodiments of the present application. Obviously, the described embodiments are only a part of the embodiments of the present application, but not all of the embodiments. Based on the embodiments in the present application, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present application.

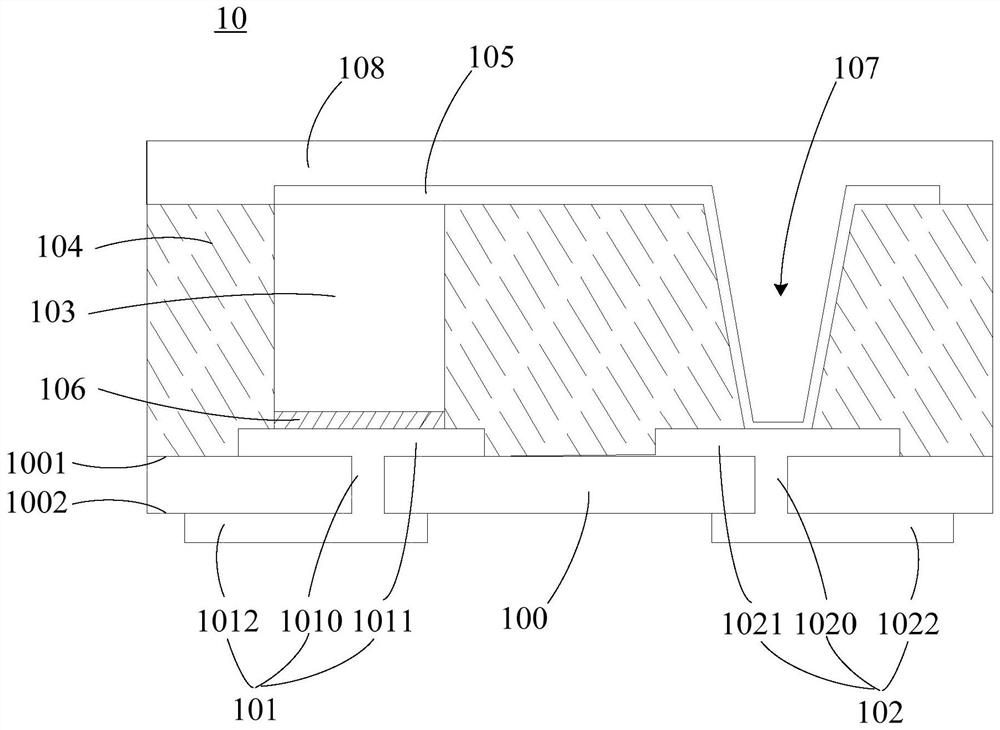

[0026] see figure 1 , figure 1It is a schematic cross-sectional structure diagram of an embodiment of the chip package of the present application. In this embodiment, the chip package 10 includes a carrier board 100 , a first pad 101 , a second pad 102 , a chip 103 , a first plastic encapsulation layer 104 and a metallization layer 105 . The carrier board 100 has opposite first surfaces 1001 and second surfaces 1002, and the carrier bo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com