I2C bus verification method and verification system

A bus verification and verification system technology, applied in the field of I2C bus verification methods and verification systems, can solve the problems of no detection function, single timing parameter settings, and inability to change, and achieve the effect of improving reliability and improving reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

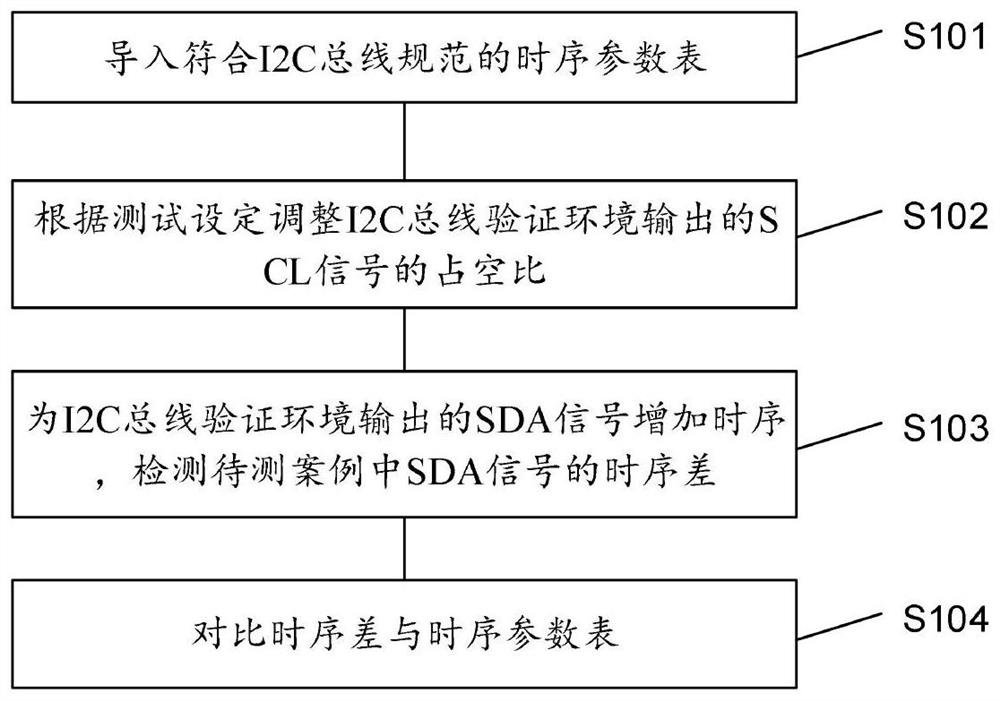

[0031] Embodiments of the present invention will now be described with reference to the drawings, in which like reference numerals represent like elements. As mentioned above, the present invention provides an I2C bus verification method and verification system. The I2C bus verification method and verification system of the present invention can dynamically adjust the duty cycle of the clock signal, satisfying a wider range of application tests, and greatly Improve the reliability of verification.

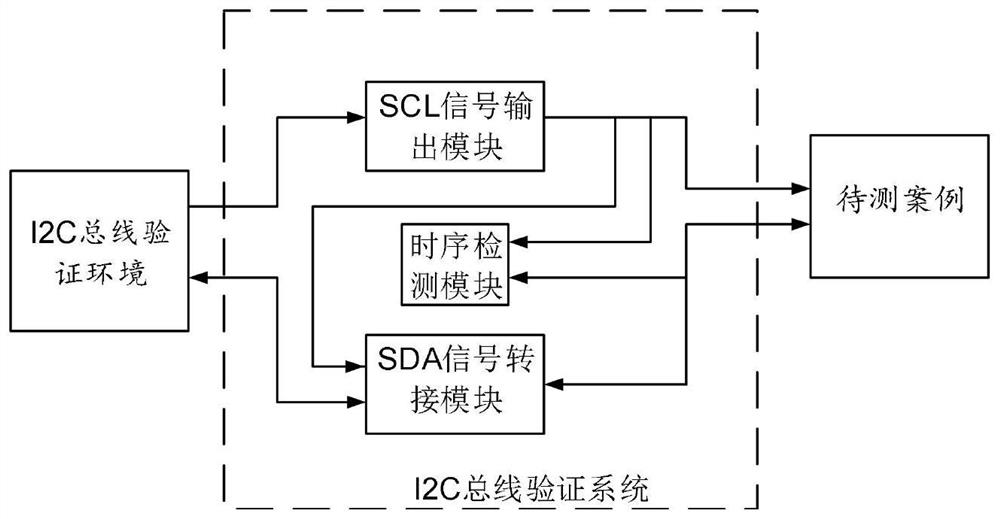

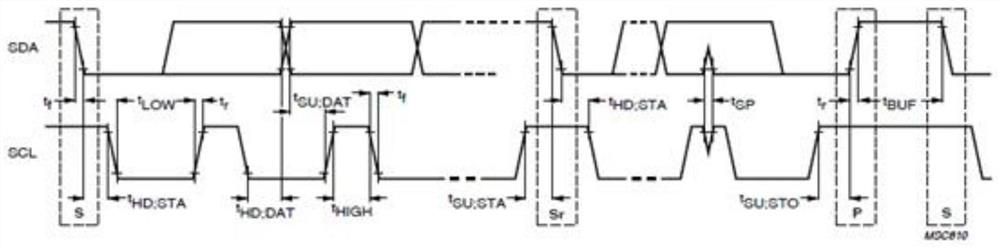

[0032] Please refer to figure 1 , figure 1 It is a structural block diagram of the I2C bus verification system of the present invention. As shown in the figure, the verification system of the I2C bus of the present invention is arranged between the I2C bus verification environment and the case to be tested, and a timing parameter table conforming to the I2C bus specification is arranged in the verification system, and the timing parameter table is as follows As shown in Table 1 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com