Clock-error estimation for two-clock electronic device

A clock error, clock technology, applied in the field of operating dual clock electronic equipment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

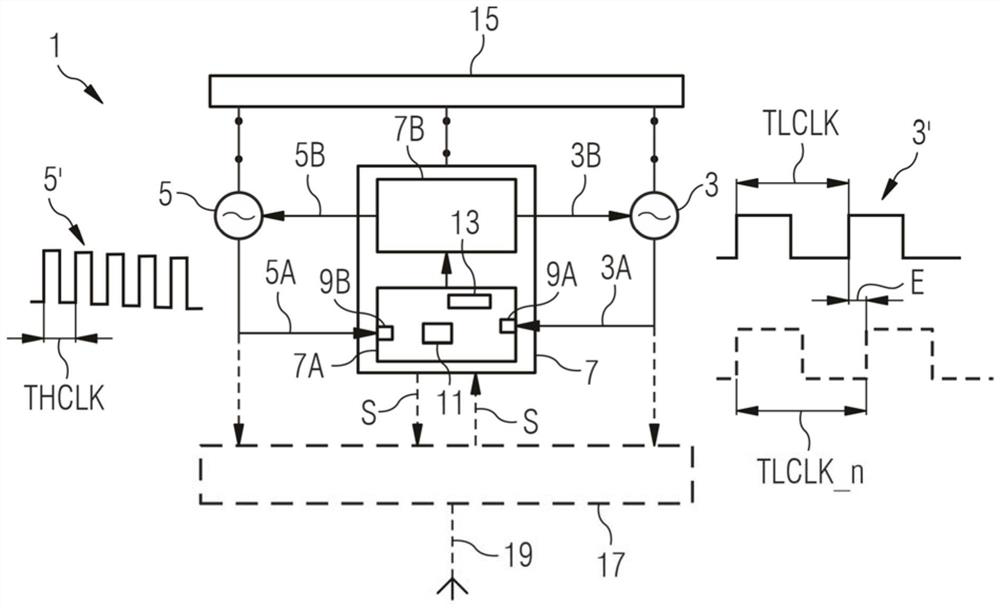

[0077] The following is a detailed description of exemplary embodiments of the present disclosure. The exemplary embodiments described herein and illustrated in the accompanying drawings are intended to teach the principles of the disclosure to enable one of ordinary skill in the art to implement and use the disclosure in many different environments and for many different applications. Therefore, the exemplary embodiments are not intended and should not be considered as a limiting description of the scope of patent protection.

[0078] Instead, the scope of patent protection shall be determined by the appended claims.

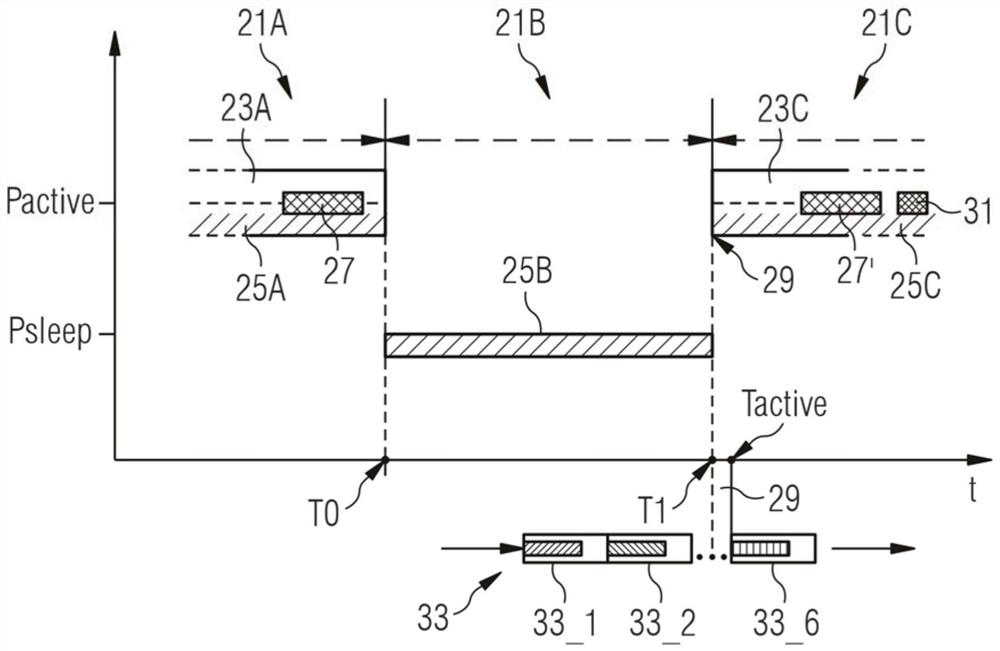

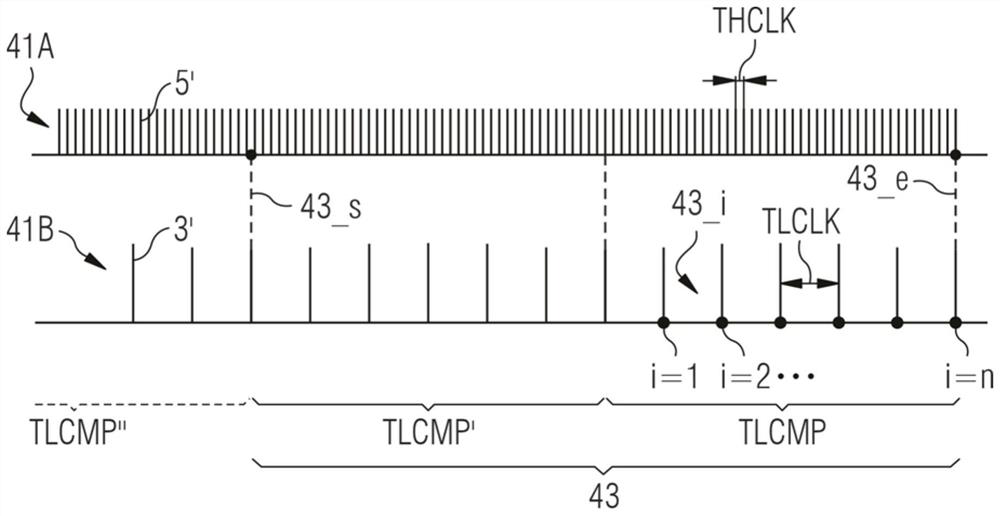

[0079] This disclosure is based in part on the realization that a particular measurement time period can improve the estimation of clock error. This improvement is achieved in particular by a specific clock counting process during the measurement time period. The inventors have particularly realized that the preferred measurement time period may be based on a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com