A Novel Reversible Circuit Synthesis Method Based on esop Representation Model

A technology of circuit synthesis and modeling, applied in computing models, calculations, quantum computers, etc., can solve problems such as high qubit numbers and achieve the effect of reducing the number of qubits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0036] This embodiment provides a novel reversible circuit synthesis method based on the ESOP representation model, comprising the following steps:

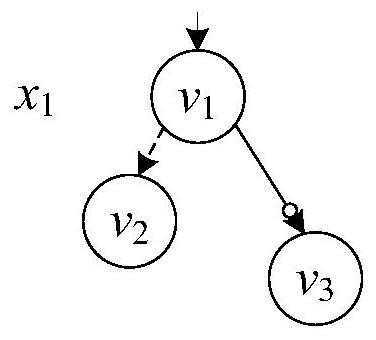

[0037] S1. Use shared function decision diagram SFDD to represent multi-output Boolean function F: {0,1} n →{0,1} m , where n input variables form the set X={x 1 ,x 2 ,…,x n }, m output functions form a set F={f 1 ,f 2 ,…,f m }; Identify each output function f of the multi-output Boolean function F according to the drawn SFDD graph G and the linear variable identification rule j the linear variable x i , so as to get the set of output functions and a set of linear variables and F LV with X LV The relationship between i.e. X LV One of the variables in is at least F LV A linear variable of a function in , similarly, F LV A function in contains at least one linear variable belonging to X LV ;

[0038] For the linear variable identification rules in the above steps, the specific rules are:

[0039] Given an SFDD ...

specific Embodiment approach

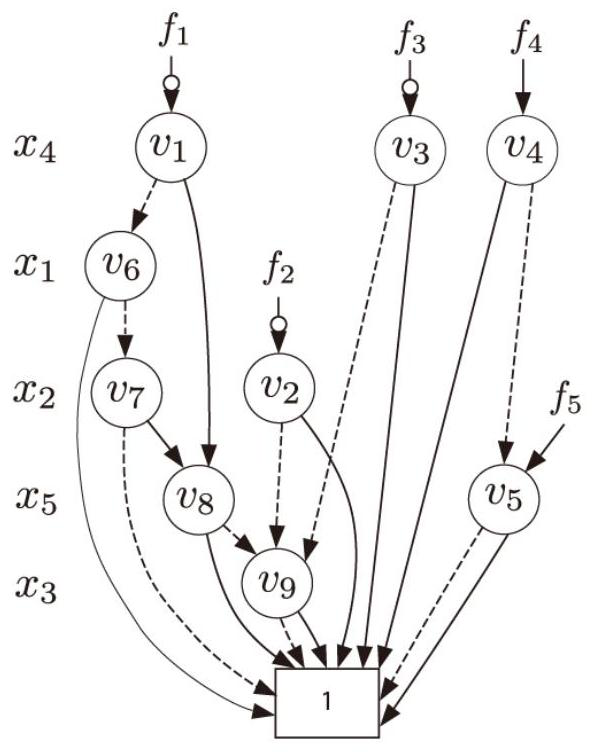

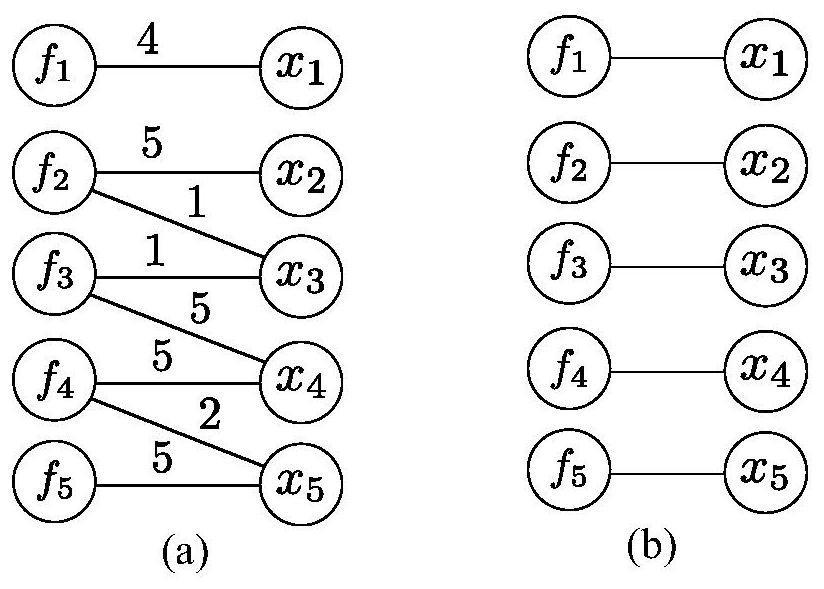

[0068] In this specific embodiment, the RevLib function mod5d2_17 is taken as an example to specifically explain the present invention.

[0069] 1) Use SFDD to identify the linear variables of each output function

[0070] The SFDD representing the function mod5d2_17 is as follows figure 2 shown in figure 2 In the SFDD shown, node v 1 ~v 5 are the output function f 1 ~f 5 the root node of , where v 1 , v 3 and v 4 Located on Tier 1 of SFDD. path and respectively represent the output function f 1 ~f 4 The longest dominating active path of the FDD, denoted f 5 The longest dominating active path of the FDD contains only the root node v 5 .

[0071] From the definition of a linear node, it can be seen that figure 2 node v in 2 ~v 6 and v 9 All are linear nodes, and they are located in the above-mentioned 5 longest dominating active paths respectively. According to the linear variable identification rule, it can be known that x 1 is f 1 Linear variable of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com