Erasing verification method and device of storage unit, computer equipment and storage medium

A technology for erasing verification and storage units, which is applied in the field of data processing, and can solve problems such as over-erasing, increasing the probability of reading errors, and the decline of cyclic erasing and writing capabilities, and achieve the effect of reducing loss and reducing the probability of reading errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

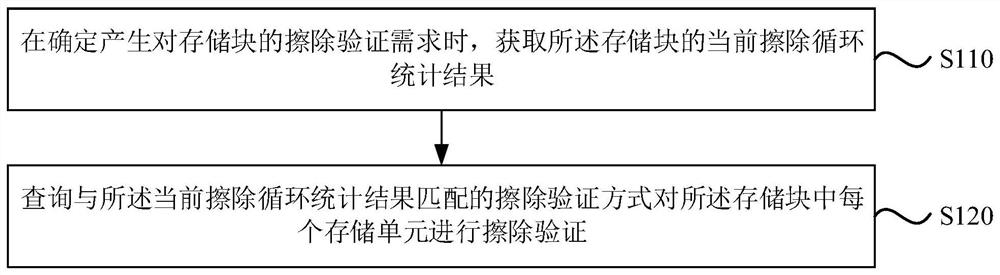

[0023] figure 1 A flow diagram of an erase verification method of a memory cell in the first embodiment of the present invention, the present embodiment can be applied to the case where the memory unit is erased after erasing, and the method can be provided by the present invention. The erase verification device of the unit is performed, and the device can be implemented in software and / or hardware, and generally integrated into electronic devices, for example, a terminal device or server or the like. Such as figure 1 As shown, the method of this embodiment includes:

[0024] S110, when it is determined that the erase verification requirements of the memory block are generated, the current erase cycle statistics of the storage block is obtained.

[0025] Specifically, in the memory, the memory block is the smallest erase unit. Typically in the memory, multiple storage units form a page (PAGE), a plurality of pages form a memory block, where the page is the smallest read / write...

Embodiment 2

[0053] figure 2 The flow chart of the erase verification method of the memory unit of the second embodiment of the present invention, the present embodiment is optimized by the above embodiment, and the query is the erase verification method that matches the current erase cycle statistics. The statistical result is compared to the preset at least one erase cycle number threshold with the preset at least one erasing cycle; in accordance with the comparison result, in the corresponding relationship between the preset comparison and the erase verification method, the current Erase the erase verification method of the loop statistics. At the same time, the erasing verification method that matches the current erase cycle statistics from the preset comparison result in the corresponding relationship of the preset comparison method and the current erase cycle statistics is queried, and the current erase cycle statistics A smaller than the first cycle number threshold, determining that t...

Embodiment 3

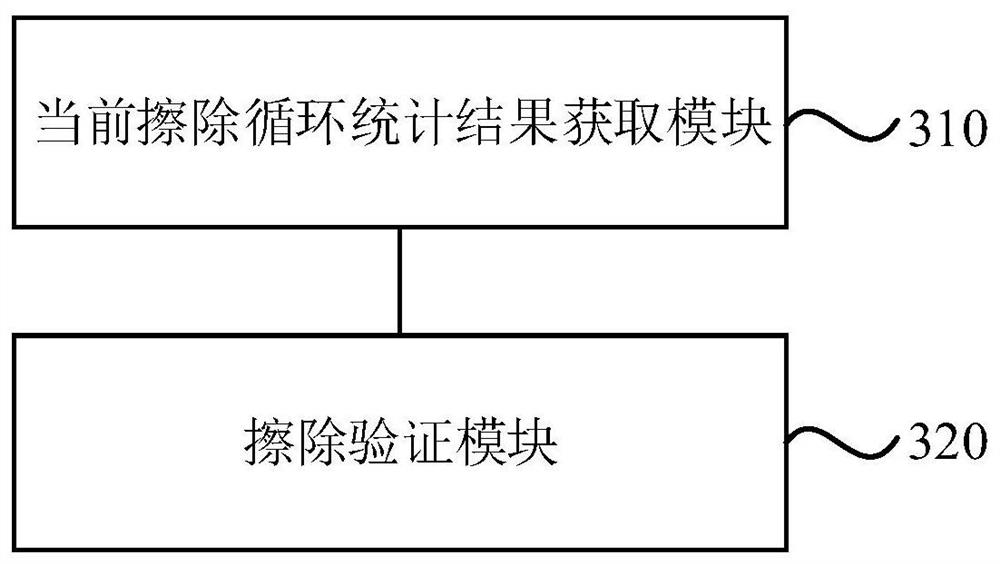

[0063] image 3 A schematic diagram of an erase verification device of a memory cell in the third embodiment of the present invention. The third embodiment is a respective device of the erasing verification method of the memory cell provided by the above embodiment of the present invention, which can be implemented in software and / or hardware, and generally integrated into electronic devices, for example, computer equipment, etc.

[0064] Accordingly, the apparatus of the present embodiment can include:

[0065] The current erase cycle statistical result acquisition module 310 is used to obtain the current erase cycle statistics of the storage block when determining the erase verification requirements of the memory block;

[0066] The erase verification module 320 is used to query the erase verification method that matches the current erase cycle statist results to erase each memory cell per memory cell.

[0067] The embodiment of the present invention performs erase verification ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com