Asynchronous test method and system based on multiple virtual PCIE cards

A technology of asynchronous testing and virtual machine, which is applied in the field of testing to achieve wide applicability, reduce the number of tests, and improve the efficiency of testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

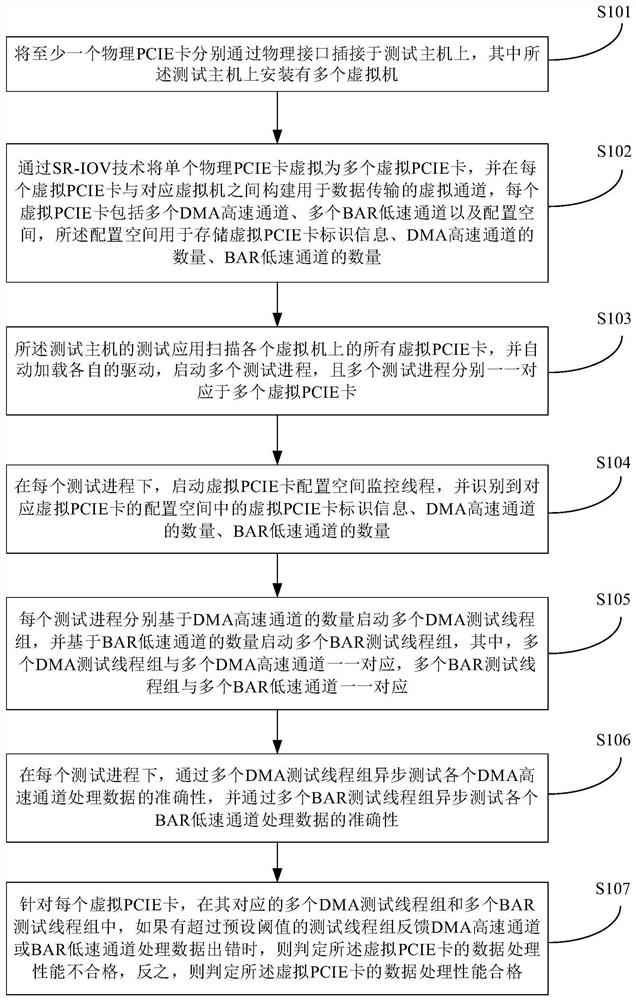

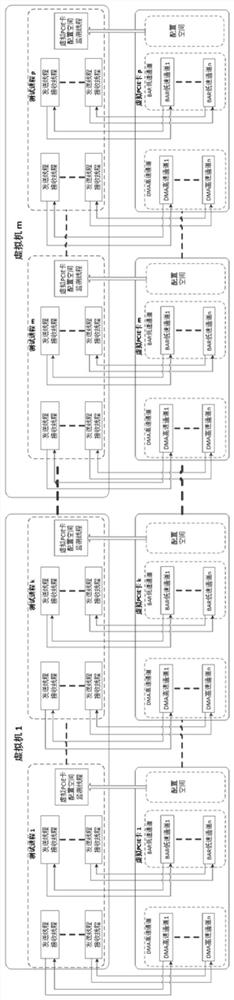

[0053] like figure 1 As shown, the embodiment of the present invention provides a kind of asynchronous testing method based on a plurality of virtual PCIE cards, and described method comprises the following steps:

[0054] S101: Plug at least one physical PCIE card into a test host through a physical interface, wherein multiple virtual machines are installed on the test host;

[0055] S102: Virtualize a single physical PCIE card into multiple virtual PCIE cards through SR-IOV technology, and construct a virtual channel for data transmission between each virtual PCIE card and the corresponding virtual machine, each virtual PCIE card includes multiple DMA high-speed channel, multiple BAR low-speed channels and configuration space, the configuration space is used to store virtual PCIE card identification information, the number of DMA high-speed channels, the number of BAR low-speed channels;

[0056] S103: The test application of the test host scans all virtual PCIE cards on ea...

Embodiment 2

[0063] On the basis of the above-mentioned embodiment 1, the difference between the embodiment of the present invention and the above-mentioned embodiment is that this embodiment further optimizes the test process in step S106, and each DMA test thread group includes A DMA sending thread for channel sending test data and a DMA receiving thread for receiving response data, each BAR test thread group includes a BAR sending thread for sending test data to the BAR low-speed channel and a BAR receiving thread for receiving response data, Specifically:

[0064] S1061: The DMA sending thread sends the DMA test data to the corresponding DMA high-speed channel, and the BAR sending thread sends the BAR test data to the corresponding BAR low-speed channel;

[0065] S1062: After the corresponding DMA high-speed channel receives the DMA test data and performs transparent transmission or processing, returns the DMA response data to the corresponding DMA receiving thread; at the same time, t...

Embodiment 3

[0068] In order to test the limit speed of each virtual PCIE card, the embodiment of the present invention also provides a kind of asynchronous testing method based on a plurality of virtual PCIE cards, and the difference from each of the above-mentioned embodiments is that the present embodiment also includes the following steps:

[0069] S108: After the data processing performance of the virtual PCIE card is determined to be qualified, test the limit speed of each DMA high-speed channel through each DMA test thread group corresponding to the test process, and test the speed limit of each BAR low-speed channel through each BAR test thread group limit speed.

[0070] As a kind of implementable mode, the limit speed of each DMA high-speed channel is tested respectively by each DMA test thread group corresponding to the test process, specifically including:

[0071] S1081: The DMA sending thread repeatedly sends DMA test data to the corresponding DMA high-speed channel according...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com