Network physical isolation gatekeeper development platform

A technology of physical isolation and development platform, which is applied in the field of communication security, can solve problems such as high cost and slow data transmission speed, and achieve the effect of good data transmission quality, stability and high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

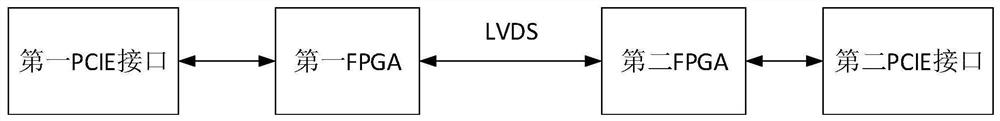

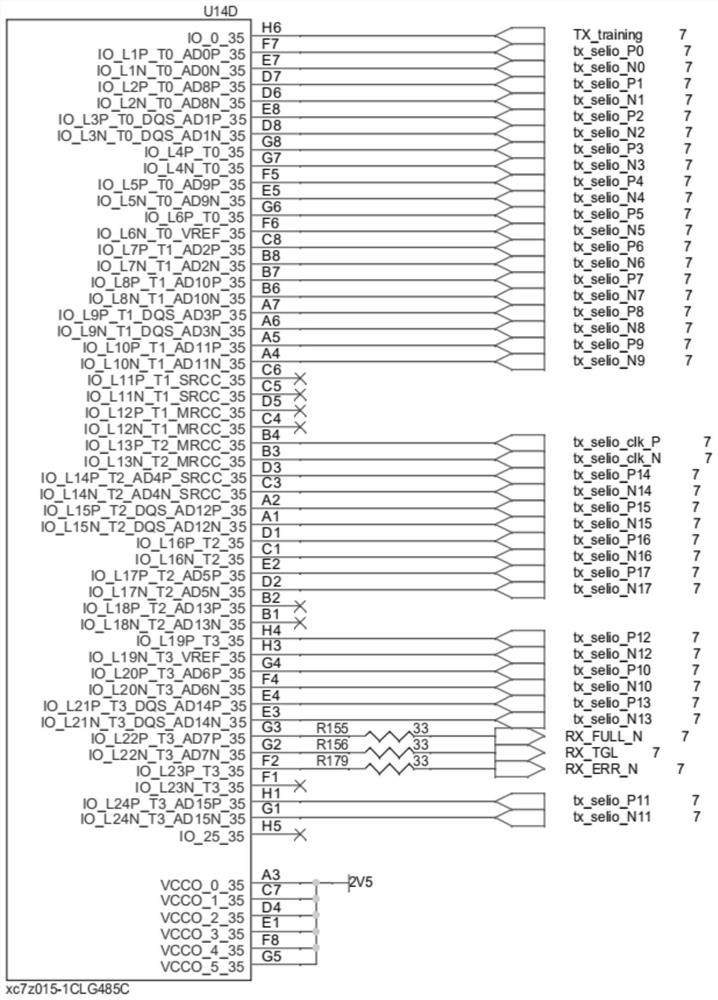

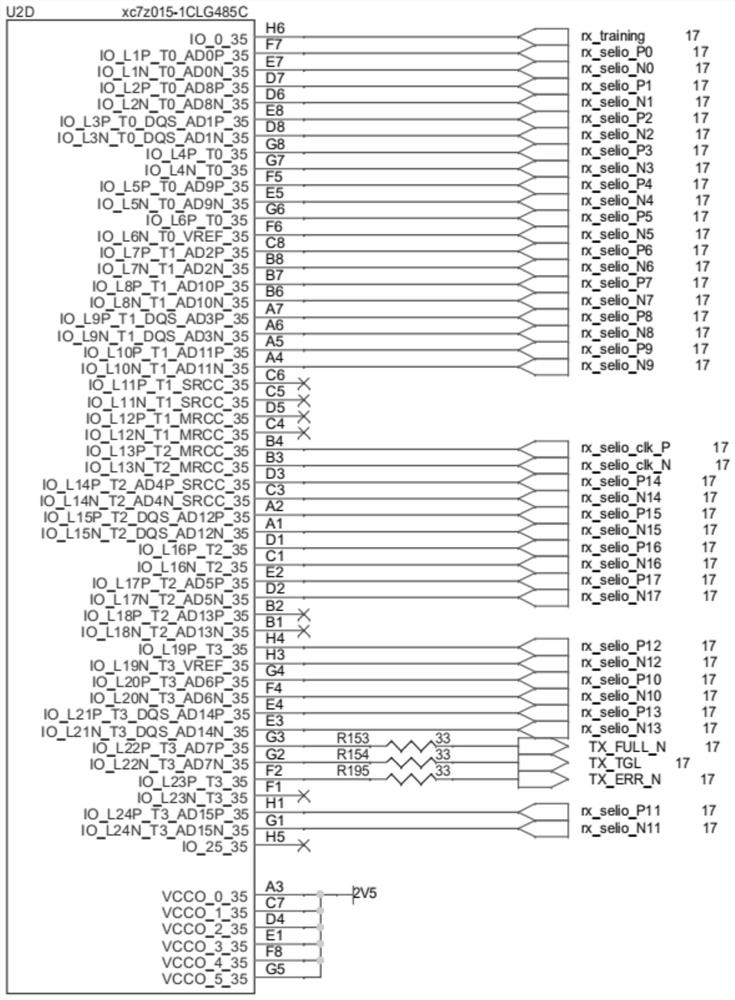

[0023] Such as figure 1 As shown, a network physical isolation gatekeeper development platform includes a physical isolation module, the physical isolation module includes a first FPGA and a second FPGA, and the first FPGA is connected to the internal network or the external network through the first PCIE interface, The second FPGA is connected to the internal network or the external network through the second PCIE interface, and the first FPGA and the second FPGA are connected through LVDS and can perform dual-channel data transmission. The models of the first FPGA and the second FPGA are both xc7z015-1CLG485C.

[0024] LVDS: Low Voltage Differential Signaling, low voltage differential signal. The LVDS transmission support rate is generally above 155Mbps (about 77MHz). LVDS is a low-swing differential signal technology that enables signals to be transmitted at a rate of several hundred Mbps on differential PCB pairs or balanced cables. Its low-voltage amplitude and low-curr...

Embodiment 2

[0029] Such as Figure 6 As shown, the difference from the above-mentioned embodiment 1 is that it also includes a first encryption and decryption unit and a second encryption and decryption unit, the first encryption and decryption unit is connected to the first FPGA, and the second encryption and decryption unit is connected to the The second FPGA connection mentioned above is used to implement the SM1 encryption and decryption algorithm. Wherein, both the first encryption and decryption unit and the second encryption and decryption unit use SSX30-D chips.

[0030] Briefly introduce the working principle of the present invention below:

[0031] The present invention is mainly used to realize the network isolation between the internal network host and the external network host. When the first FPGA is connected to the external network host, the data of the external network host is transmitted to the first FPGA through the first PCIE interface, and the first FPGA passes the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com