A method and device for realizing 32-bit integer division with high precision and low delay

A low-latency, high-precision technology, applied in complex mathematical operations, electrical digital data processing, digital data processing components, etc., can solve the problem of large intermediate bit width of the operator, occupying a lot of storage space, and large output result bit width, etc. Achieve the effect of small output bit width, increase operation delay, and reduce calculation bit width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

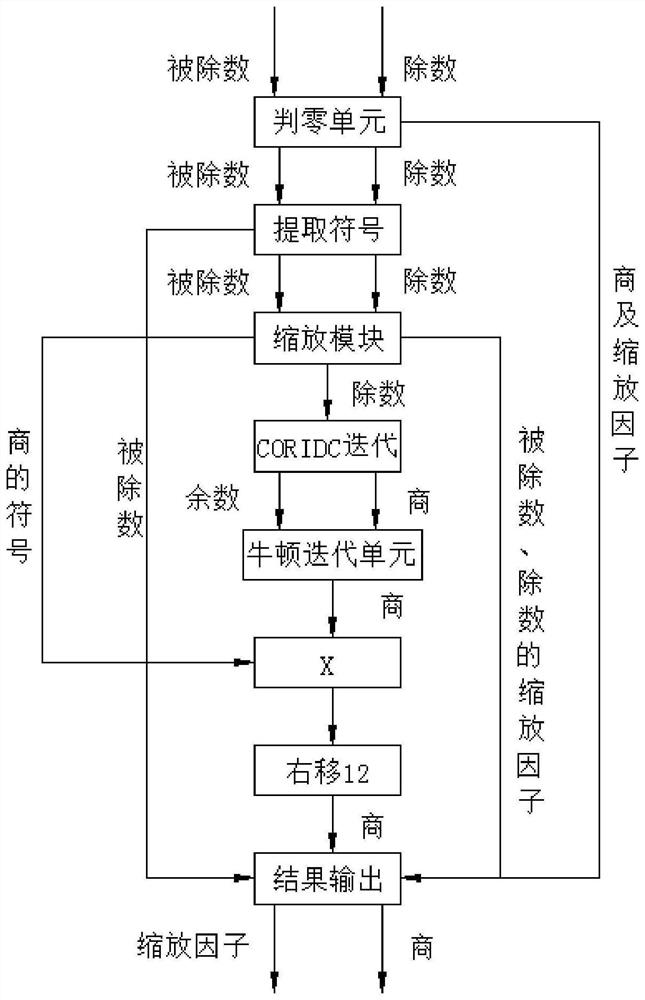

[0039] Implementation 1: Refer to Figure 1-4 : A method for realizing 32-bit integer division with high precision and low delay. It is often used in the field of digital signal processing, such as signal normalization and channel estimation. The implementation steps of this method are as follows:

[0040] Step 1: Input the dividend and the divisor into the zero judgment unit. If the dividend is 0, the quotient will output 0 directly, and the scaling factor will be 0. If the dividend is not 0, the divisor will be 0, and the quotient will be directly output as 4095, and the shift factor will be 20. If The dividend and the divisor are not 0, enter the next step.

[0041] Step 2: Output the dividend and divisor of 1, input the symbol extraction module, output the sign of the quotient and the modulus of the dividend and divisor.

[0042] Step 3: Input the dividend and divisor output by 2 into the scaling module, realize scaling the dividend and divisor to an effective bit number ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com