Circuit board via hole impedance optimization method and circuit board

An optimization method and circuit board technology, applied in printed circuit, printed circuit manufacturing, computer design circuit, etc., can solve problems such as high process cost, affecting the integrity of transmission signals, and inability to completely remove via stubs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

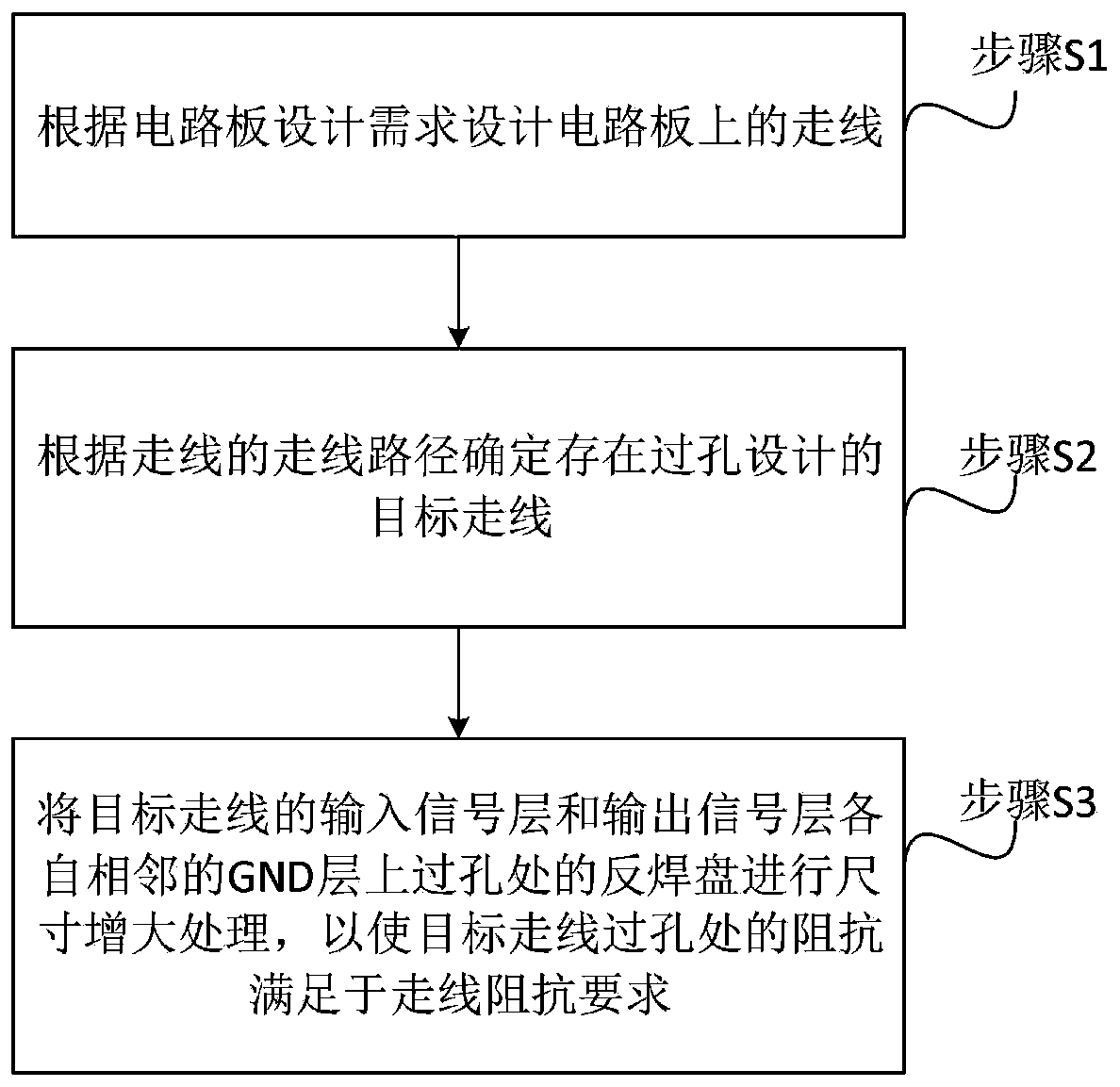

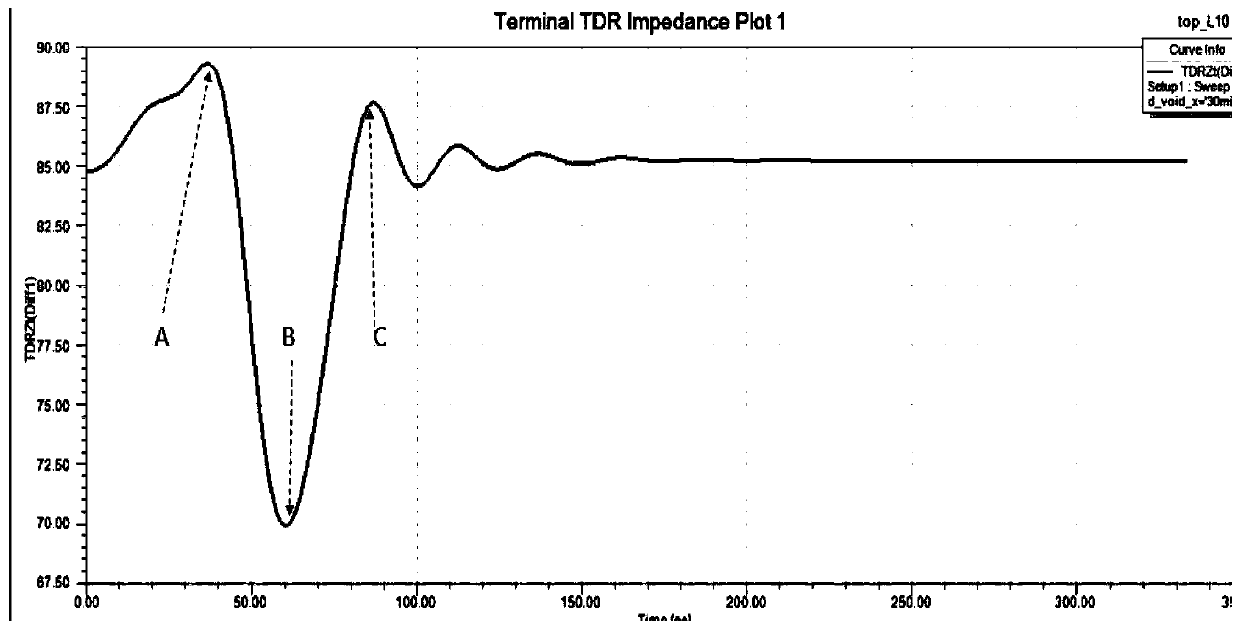

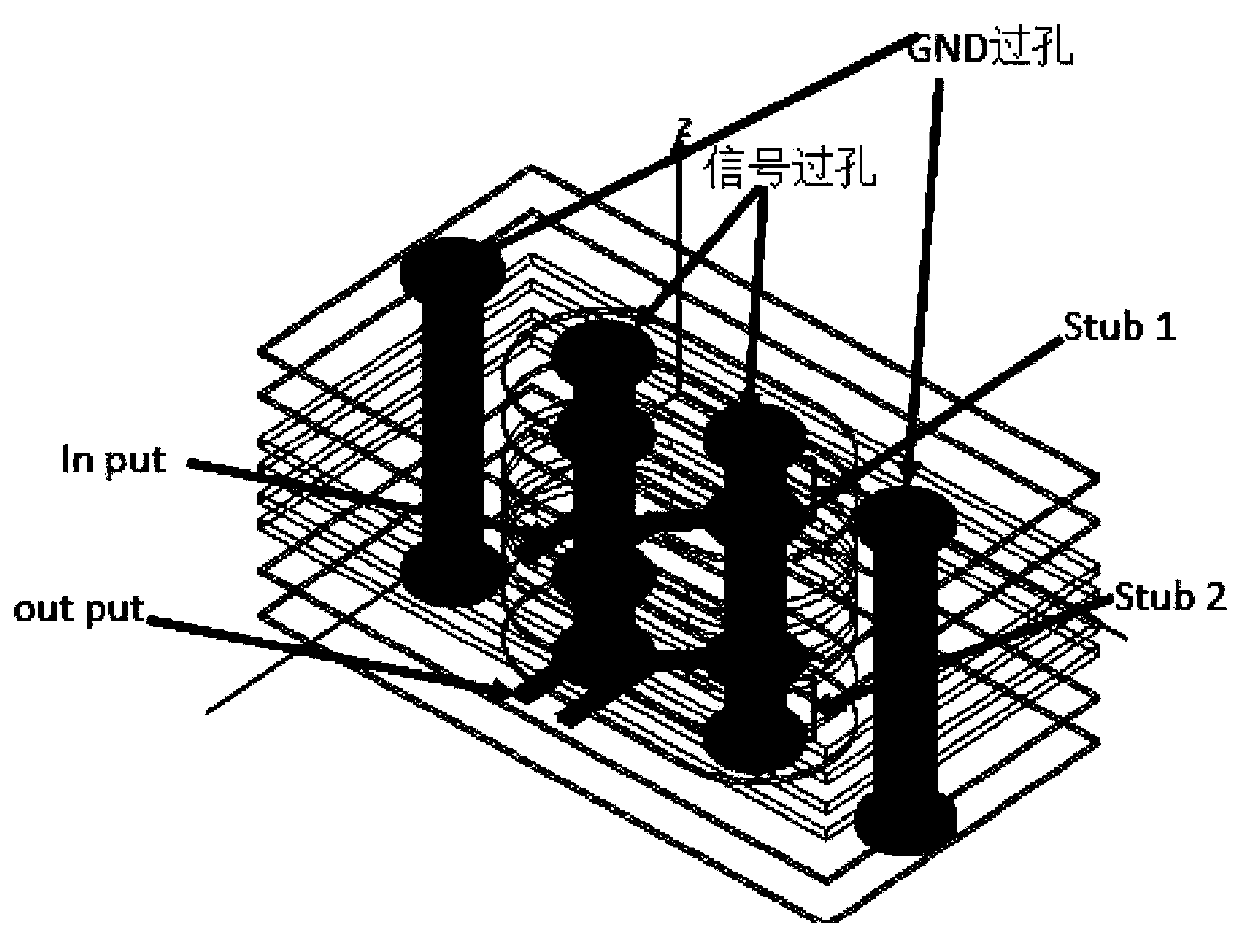

[0037] The core of the present invention is to provide a circuit board via impedance optimization method and circuit board, by changing the shape of the anti-pad at the wiring via to optimize the impedance continuity at the via, so as not to increase the process cost. It satisfies the integrity requirements of the transmission signal; moreover, this application changes the shape of the anti-pad at the via on the adjacent GND layer of the input signal layer and the output signal layer of the trace, while optimizing the impedance at the via Will not affect the impedance of the trace.

[0038] In order to make the objectives, technical solutions, and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be described clearly and completely in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of the embodiments of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com