Simulation test system of 1553B bus

A simulation test and bus technology, applied in the computer field, can solve the problems of real-time accuracy deterioration, low real-time performance, high hardware cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

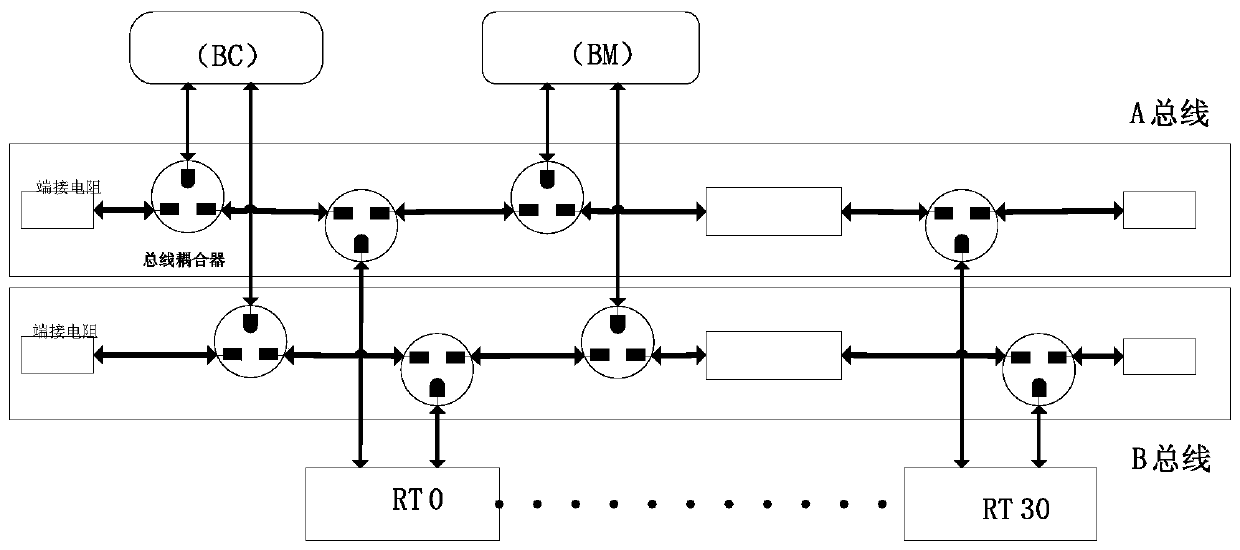

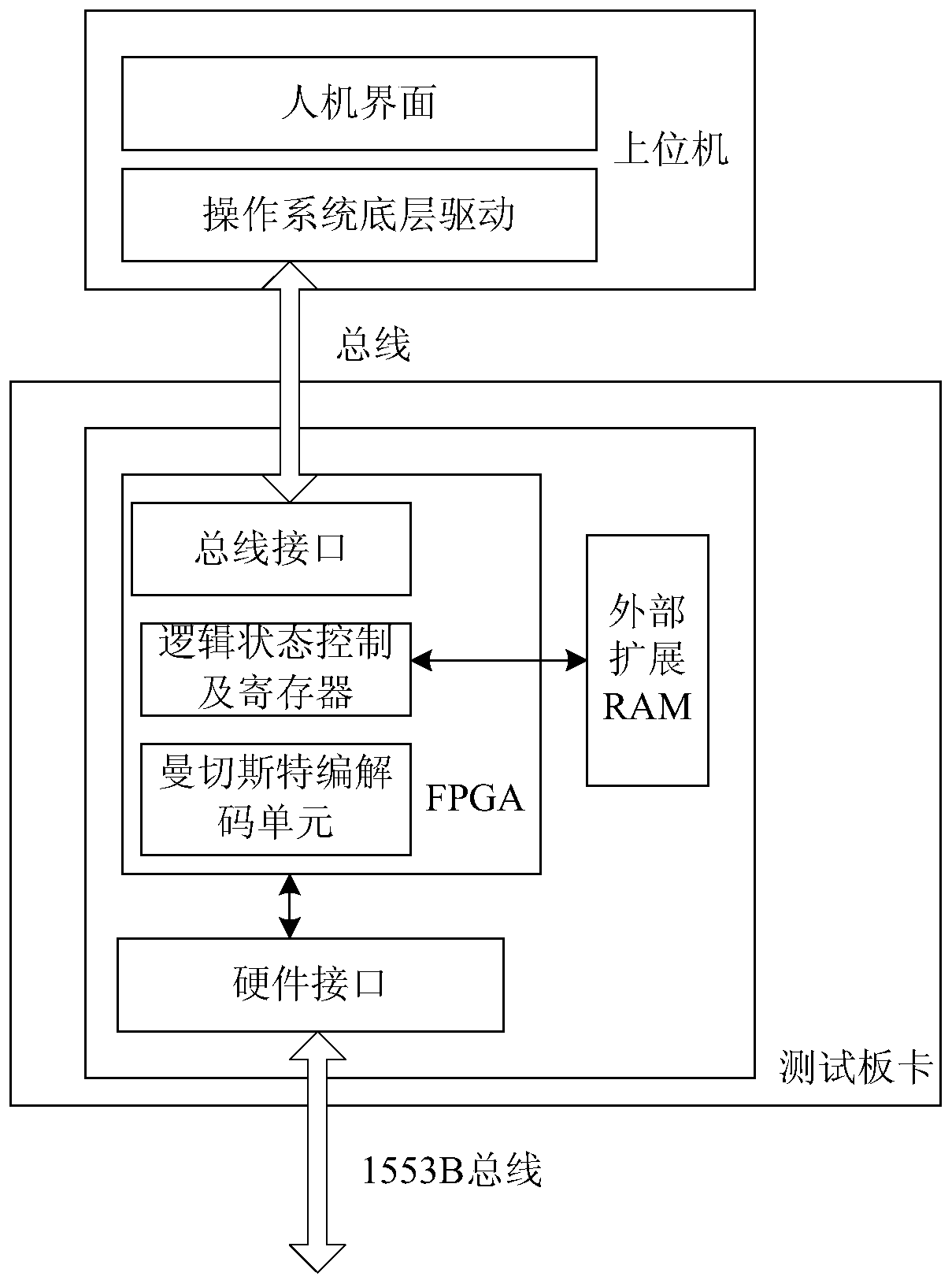

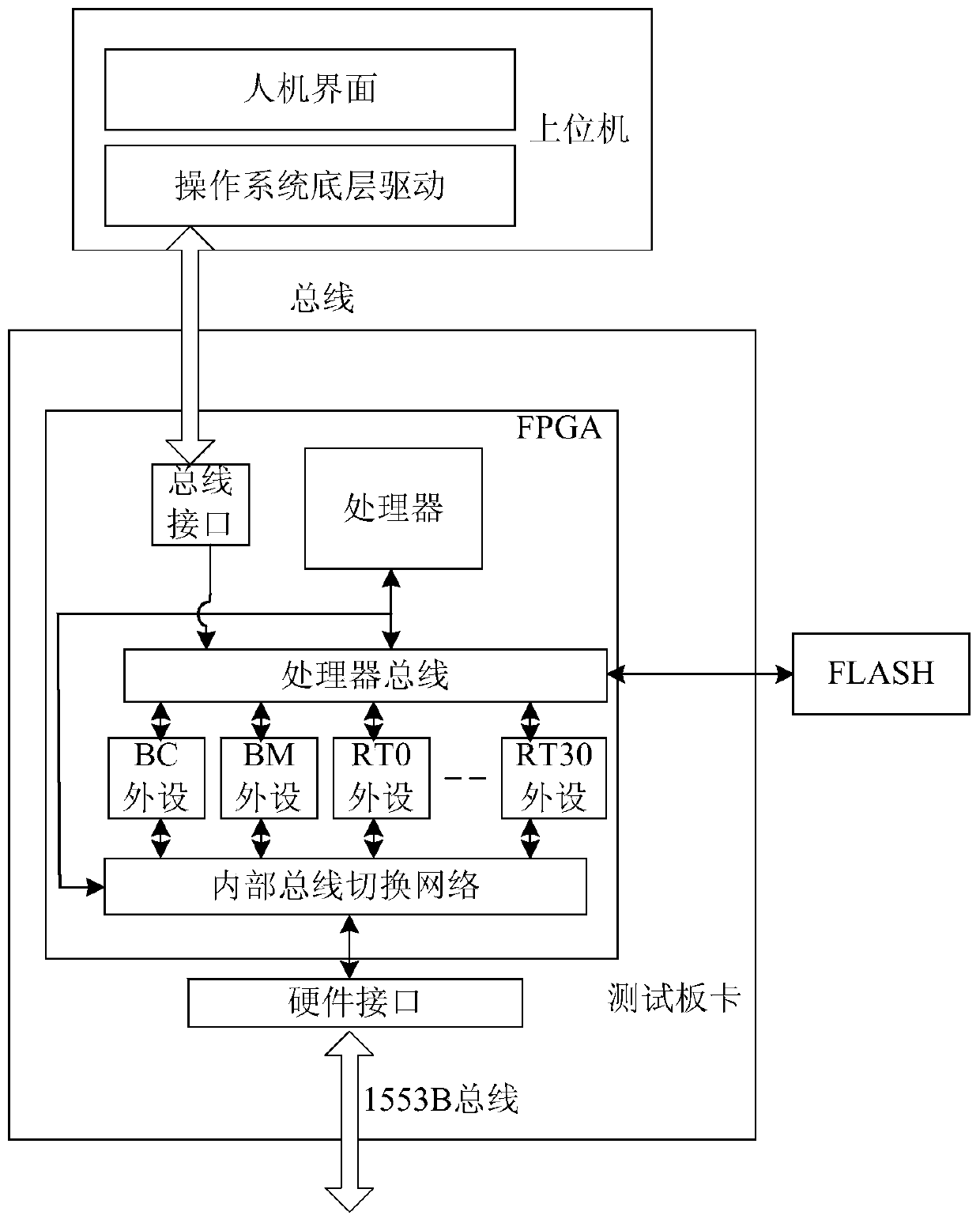

[0032]Embodiments of the present invention adopt SOC technology to construct test boards, and the constructed test boards can be truly simulated in a low-cost manner by separating the interface configuration software carried by the host computer from the real-time embedded operating software in the SOC of the test boards. A full-featured emulation test system supporting 1553B bus. Therefore, the embodiment of the present invention fully implements the simulation test of the 1553B bus.

[0033] The embodiment of the present invention makes full use of the characteristics of high integration and high flexibility of the SOC technology, constructs the intellectual property (IP) core of the standard 1553B bus on the test board, specifically adopts the FPGA t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com