Method and system for expanding number of bus channels based on GPIO

A technology for expanding the bus and channels, applied in the field of expanding the number of bus channels based on GPIO, can solve the problems of low system reliability and low access efficiency, simplify access procedures, avoid read and write operation delays, and improve reliability and stability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

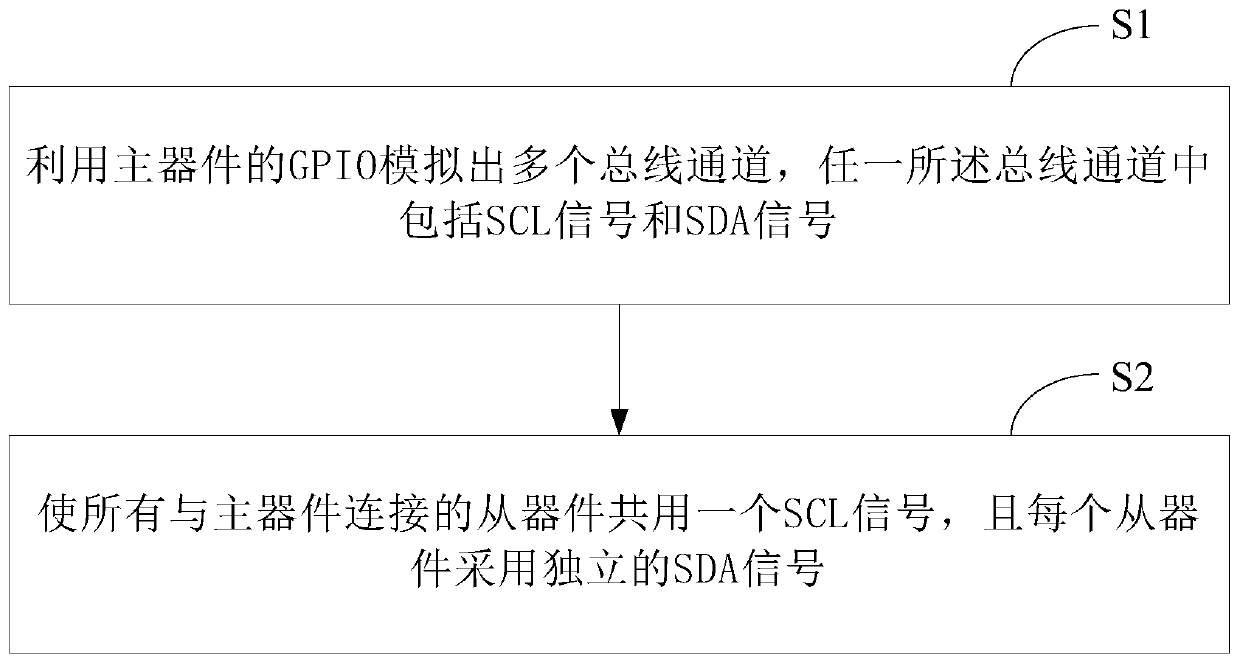

[0030] see figure 1 , figure 1 A method for expanding the number of bus channels based on GPIO provided by the embodiment of the present application, the method mainly includes the following process:

[0031] S1: Use the GPIO of the master device to simulate multiple bus channels, any bus channel includes SCL signal and SDA signal.

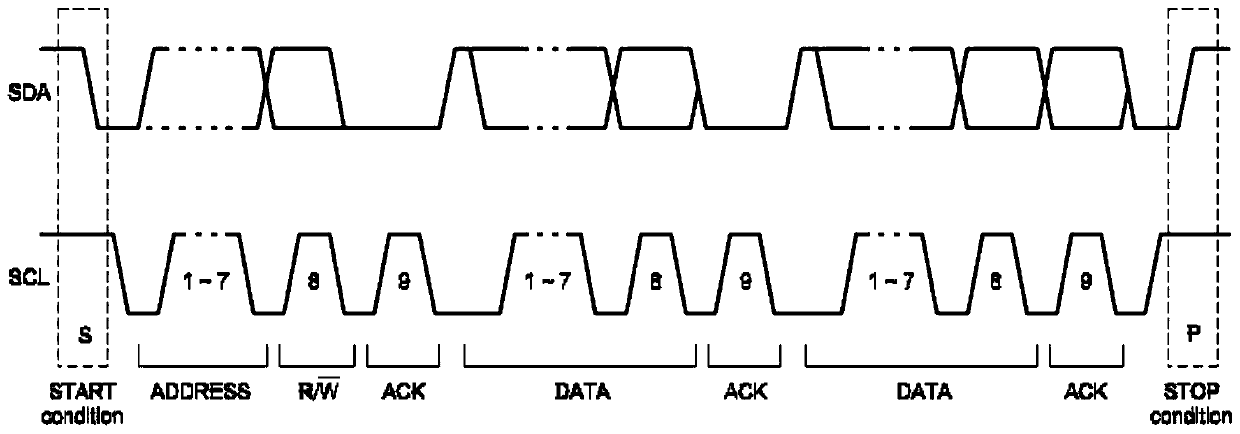

[0032] In this embodiment, the bus channel includes an I2C channel or an SMBus channel. Taking the I2C channel as an example for the bus channel, the method of step S1 is: use the GPIO of the I2C master device to simulate multiple I2C channels, and any I2C channel includes SCL signal and SDA signal.

[0033] Since the method in this embodiment is common to the I2C bus and the SMBus bus, when implementing the method in this application, in most cases, the I2C bus and the SMBus bus may not be distinguished. The main difference between the two is that the bus frequency is different. The maximum bus frequency of SMBus is lower than the bus frequenc...

Embodiment 2

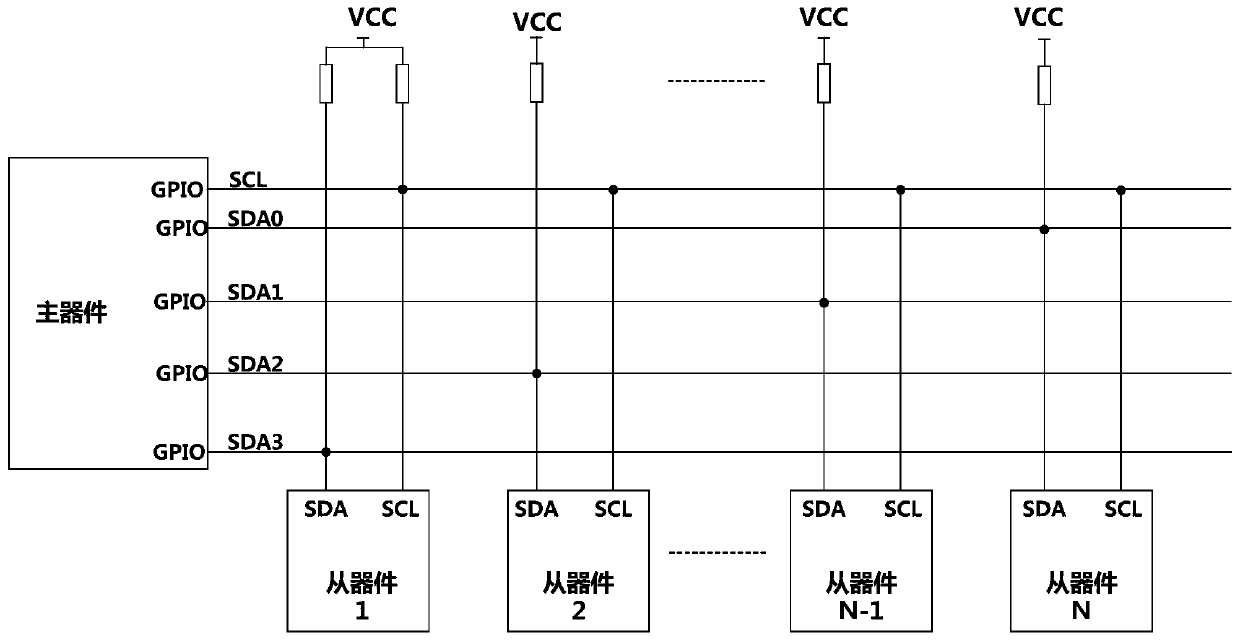

[0049] exist figure 1 with figure 2 On the basis of the illustrated embodiment see image 3 , image 3 It is a schematic structural diagram of a system for expanding the number of bus channels based on GPIO provided in the embodiment of the present application. Depend on image 3 It can be seen that the system for expanding the number of bus channels based on GPIO in this embodiment includes: a master device, multiple slave devices, multiple bus channels, and multiple pull-up resistors. Wherein, the master device is provided with multiple GPIOs, and the master device is connected to one or more slave devices through any bus channel. Any bus channel includes an SCL signal and an SDA signal, and the SCL signals in multiple bus channels are the same and the SDA signals are different. Each pull-up resistor is matched with an SCL signal or an SDA signal. Specifically, the SDA signal in each bus channel is connected with a pull-up resistor. Since all bus channels share an SCL ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com