Robust design method for non-standard input vesa timing sequence

A design method and a robust technology, applied in the field of video processing, can solve problems such as abnormal output images, bad processing methods, and robustness of output images, and achieve the effects of solving logic processing problems, easy hardware logic implementation, and clear design structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

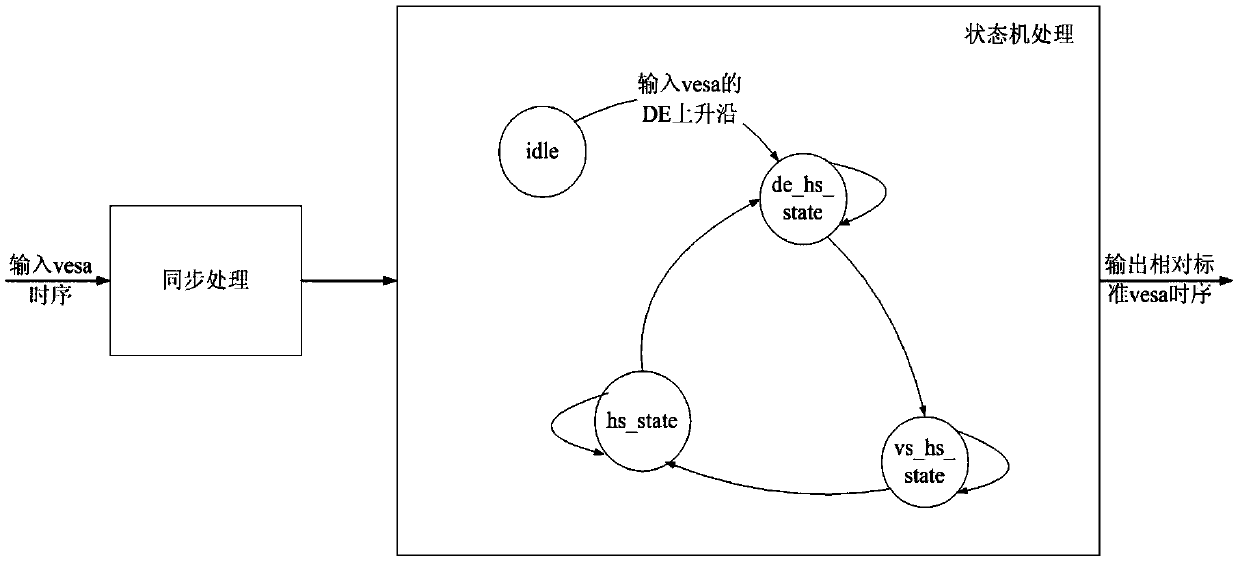

Method used

Image

Examples

Embodiment Construction

[0022] Embodiments of the present invention are described in detail below, and the embodiments are exemplary and intended to explain the present invention, but should not be construed as limiting the present invention.

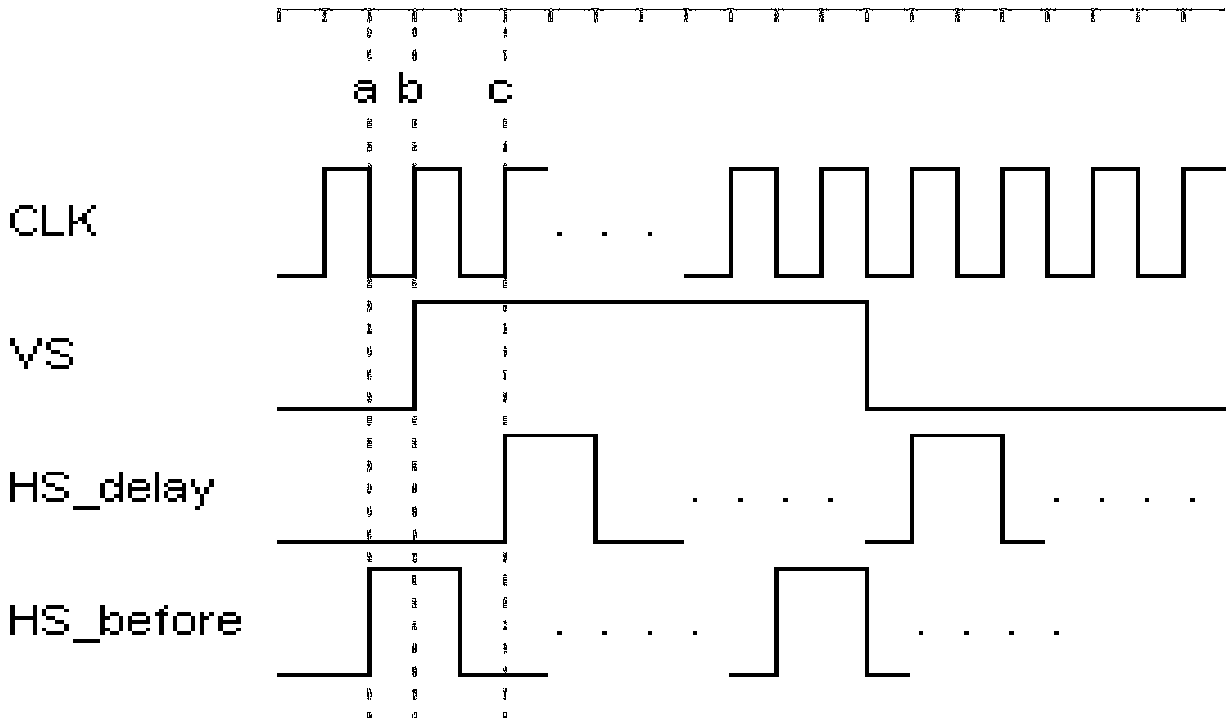

[0023] In the standard vesa timing, VS, HS, and DE have strict timing correspondence. However, in the actual circuit, the input VESA timing does not fully meet the VESA timing standard. The common non-standard input VESA timing has the following situations (take the resolution of 1280*1024@60Hz as an example):

[0024] 1. VS and HS do not change to high level at the same clock rising edge;

[0025] 2. One line is not equal to 1688 clock cycles (the number of effective pixels is 1280);

[0026] 3. The number of lines in the blanking period is not equal to 42 lines (the effective number of DE lines is 1024);

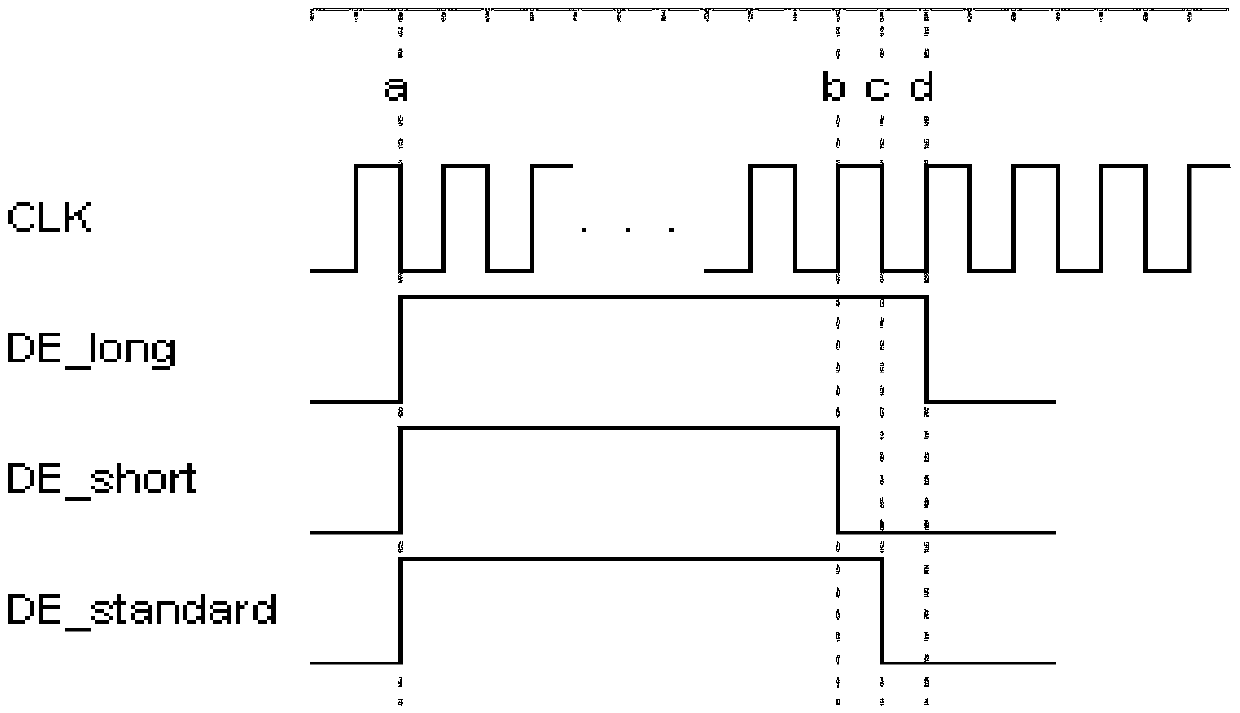

[0027] 4. DE high level time is not equal to 1280 clocks.

[0028] 5. The number of input lines is not equal to 1024 lines.

[0029] Due to the logic ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com