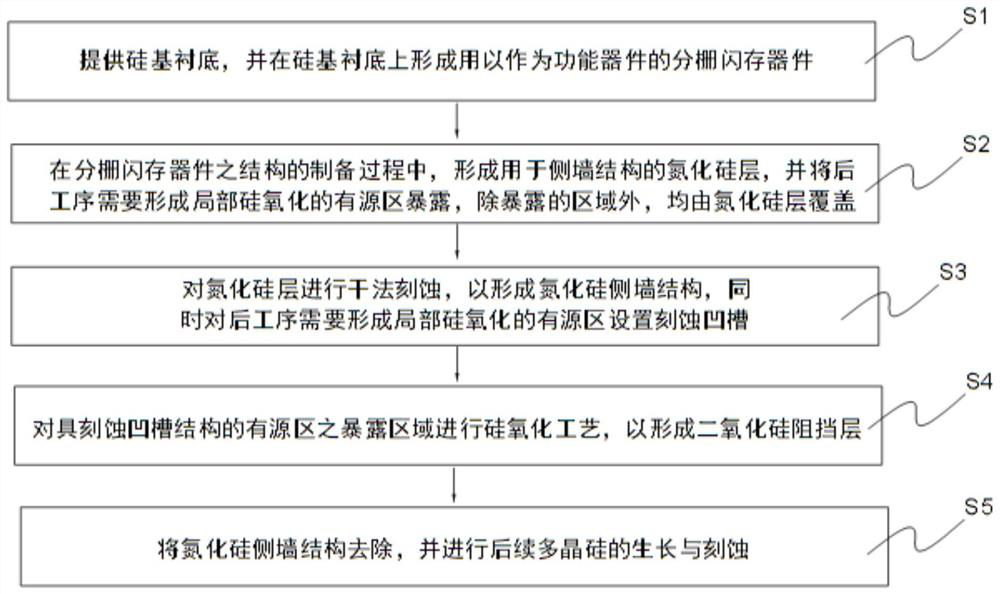

Process integration method for improving multi-step polysilicon etching damage in split-gate flash memory

An integrated method and polysilicon technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of easy etching of silicon dioxide film, etching damage of active area, economic loss, etc., and achieve the goal of reducing etching damage risk, avoid etching damage in the active area, and improve stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

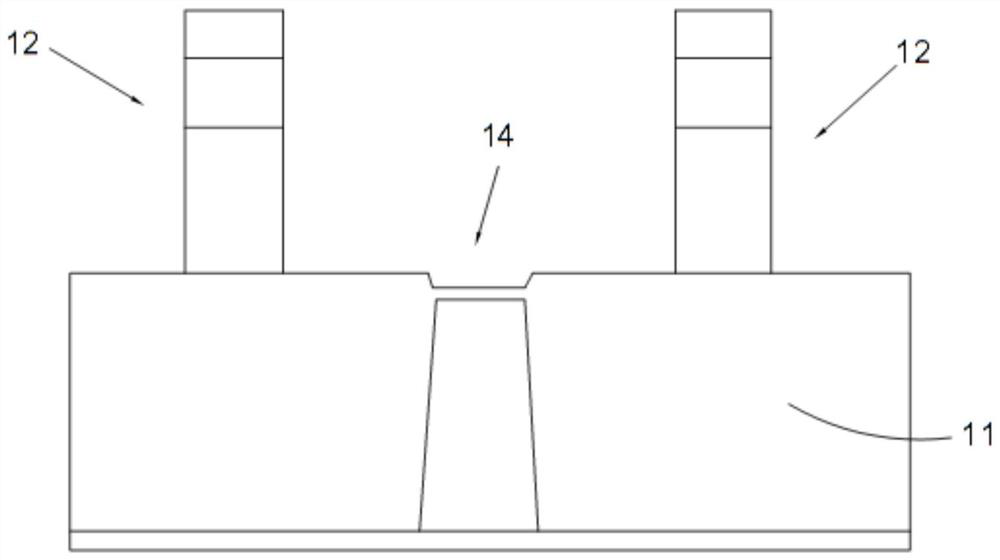

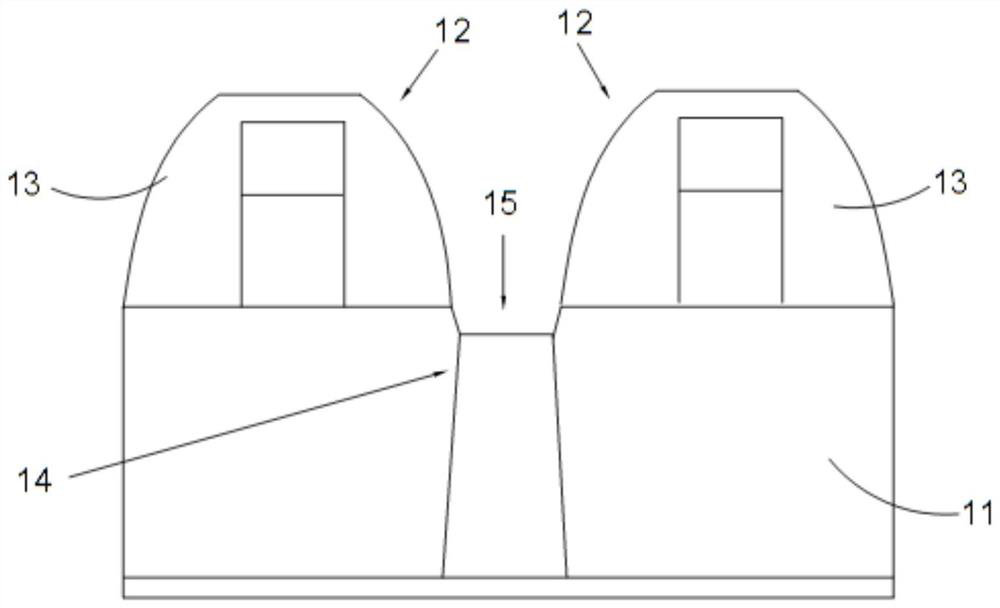

[0026] In order to illustrate the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

[0027] Due to its advantages of high density, low price, and electrical programmability and erasability, flash memory has been widely used as the best choice for non-volatile memory applications. At present, the floating-gate non-volatile flash memory is mainly divided into two types according to its structure: ETOX flash memory and split-gate flash memory. The main difference between the two lies in the programming / erasing method and cell structure. The programming / erasing method of ETOX flash memory is: channel hot electron injection / FN tunneling method, and the split-gate flash memory is: source channel hot electron Injection / field-enhanced poly-to-poly FN tunneling method; structurally, ETOX flash memory is a stacked gate structure, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com