A control method and device for reducing programming interference

A technology of programming interference and control method, applied in the field of memory devices, can solve problems such as failure to achieve expected results, difficulty in reaching voltage, and insufficient precharge.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

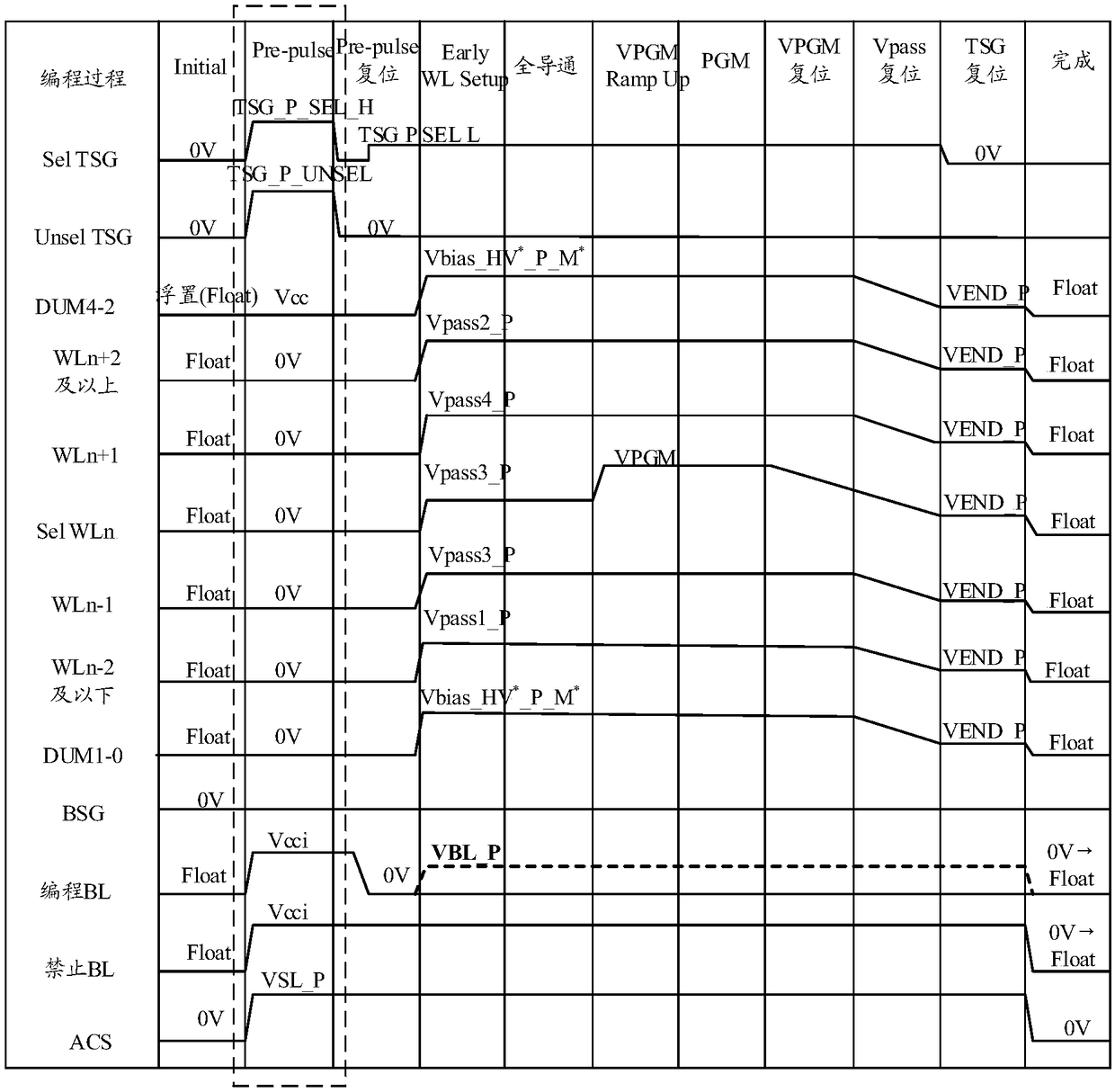

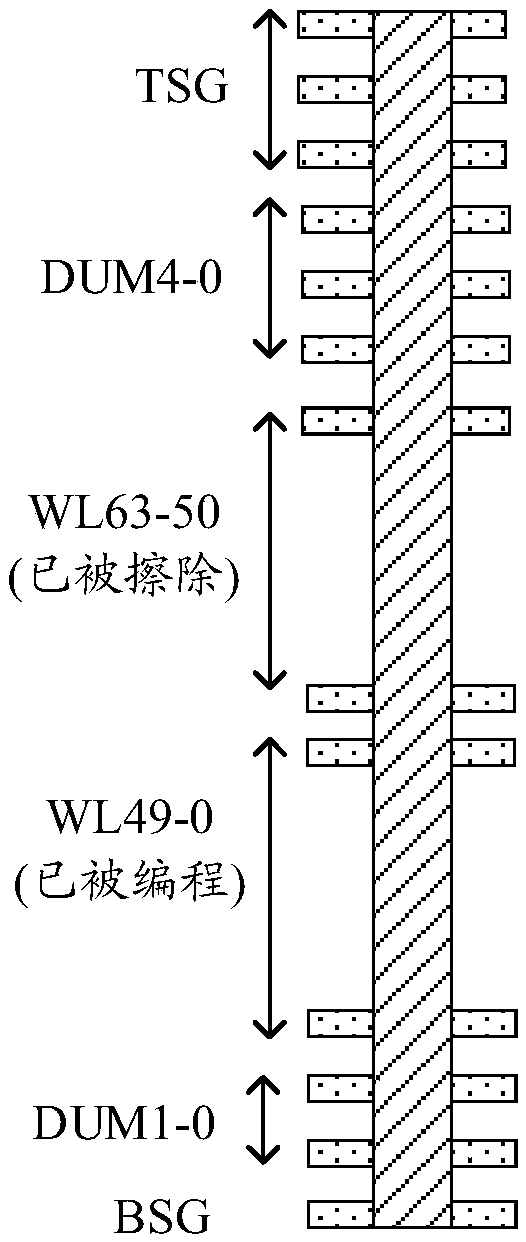

[0067] like Figure 4 As shown, the control method for reducing programming disturb provided by Embodiment 1 of the present invention is a control method for performing precharging from both sides of the drain terminal and the P well terminal at the same time. The arrows in the figure show the direction of hole injection.

[0068] combine Figure 5 It can be seen that in this embodiment, in the pre-charging stage of the storage device (that is, the stage of loading the pre-pulse Pre-pulse in the figure), the top gate TSG0-5 is loaded with a high potential that can be turned on by TSG0-5; The power supply potential Vcc is loaded on the BL, so that holes are injected into the channel hole from the drain terminal, and the potential of the channel hole is increased. At the same time, the bottom gate BSG is connected to the ground potential GND, and the power supply potential Vcc is applied to the Pwell; since the potential GND of the bottom gate BSG is lower than the potential V...

Embodiment 2

[0072] like Image 6 As shown, the control method for reducing program disturb provided by Embodiment 2 of the present invention is a control method for precharging only from the P-well terminal. The arrows in the figure show the direction of hole injection.

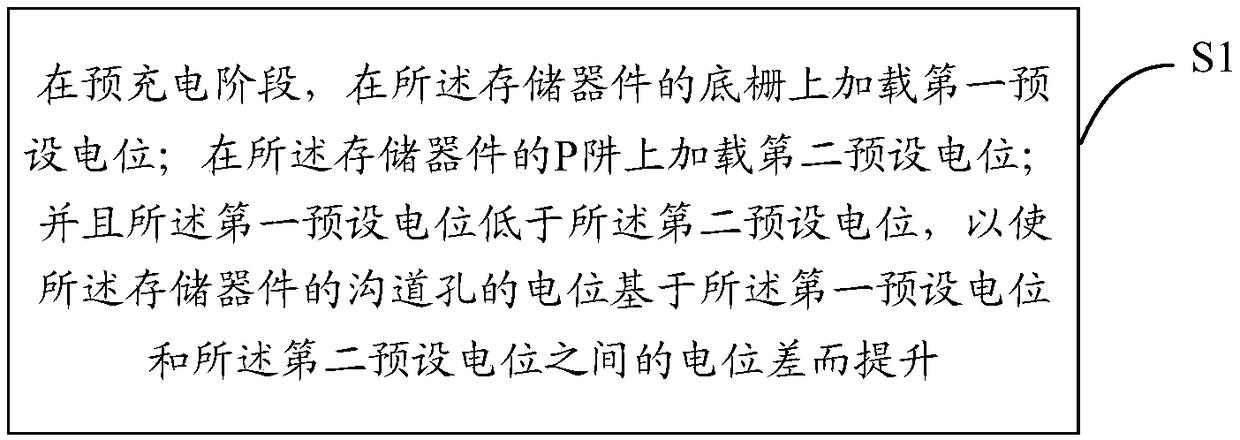

[0073] combine Figure 7 It can be seen that in this embodiment, in the precharging stage of the storage device (that is, the stage of applying the pre-pulse Pre-pulse in the figure), the bottom gate BSG is connected to the ground potential GND, and a bias voltage higher than the power supply potential is applied to the Pwell. Position bias; since the bottom gate BSG potential GND is lower than the Pwell potential bias, holes in the Pwell are injected into the channel holes. At the same time, the top gate TSG0-5 is grounded, so that the top gate is in a closed state; the bit line BL is floating (Float).

[0074] Here, the precharged voltage at the P-well terminal may not be affected by the bit line terminal (ie, the d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com