A ldpc decoder based on random bit stream update

A random bit and decoder technology, applied in the field of LDPC decoders, can solve the problems of insufficient optimization of variable node update module design, redundant resource and architecture design, slow convergence speed, etc., to improve the operating clock frequency and data. Throughput, less unit resource occupancy, and reduced wiring difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will be further described below in conjunction with the accompanying drawings.

[0038] figure 1 It is an embodiment of an LDPC decoder based on random bit stream update described in the present invention. Each box represents a unit, and each unit is composed of different implementation components. The bold arrows indicate the data flow interaction, and the numbers above the arrows indicate the width of the data flow.

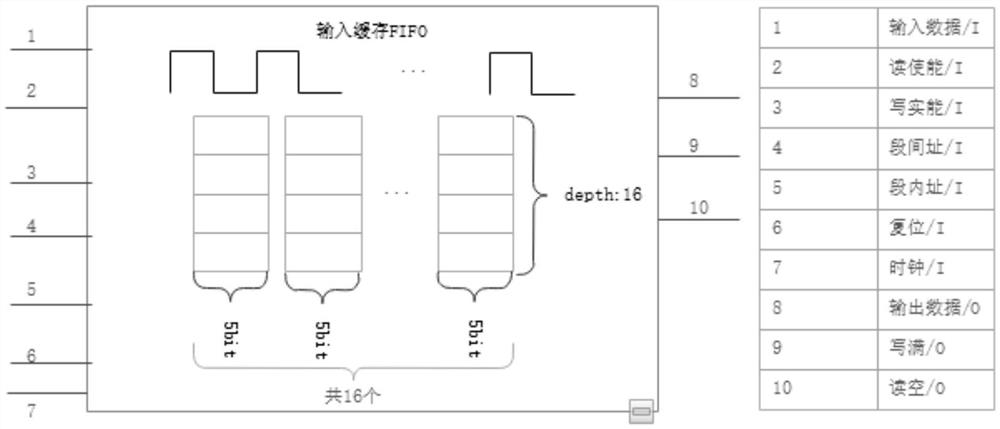

[0039] figure 2 It is an implementation method of using asynchronous FIFO for the input buffer unit, with a total depth of 256, a width of 5 bits, and different input and output bit widths. The input enters 40 bits per clock, occupying 8 FIFO units in total. 5 bits represent a received channel symbol amplitude, that is, quantized into 5 bits. FIFO outputs 80 bits per clock. In this way, for the 672-length LDPC code defined in 802.11ad, the input buffer is completed in 84 clock cycles, and the output of a code block is complete...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com