Digital Waveform Test Method of Integrated Circuit Tester

A technology of digital waveforms and testing methods, which is applied to components, instruments, and measuring electronics of electrical measuring instruments. It can solve the problems of large device footprint, long development time, and high power consumption, so as to increase power consumption and reduce design cycles. , The effect of reducing development time and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Below in conjunction with accompanying drawing, the present invention is described in further detail.

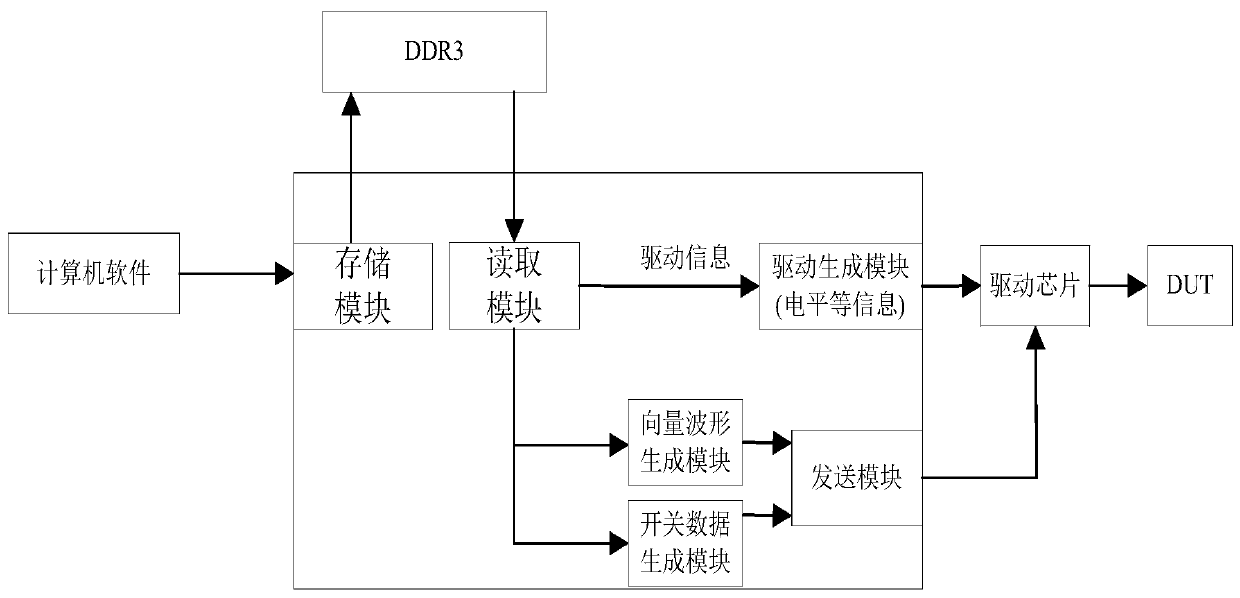

[0026] Such as figure 1 As shown, the present invention provides a digital waveform test system of an integrated circuit tester, including a storage module, a reading module, a vector waveform generation module, a switch data generation module, a drive generation module, and a transmission module;

[0027] The storage module: storing vector information, cycle information, edge positioning information, and driving information data sent by the host computer;

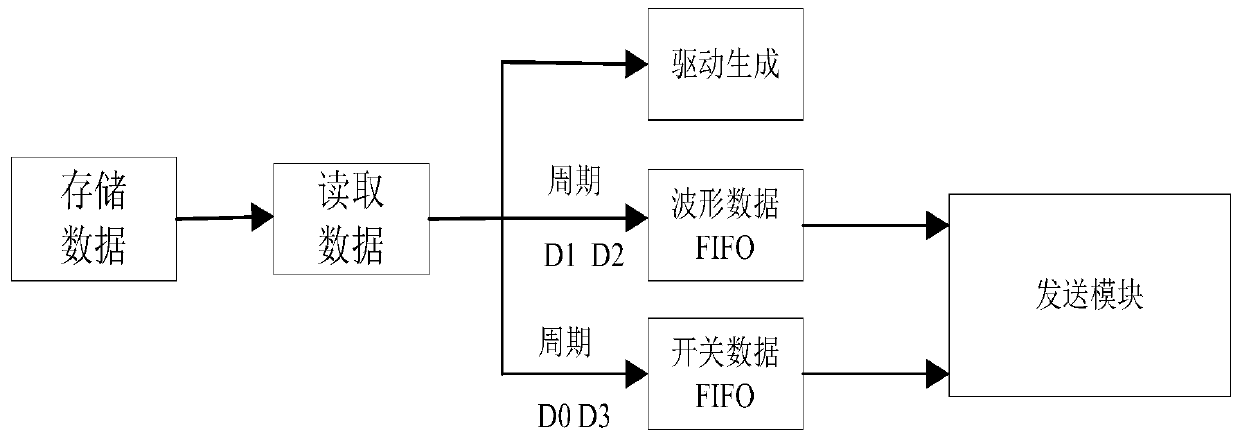

[0028] The reading module: read vector, period, edge positioning information, and drive information to the vector waveform generation module, switch data generation module, and drive generation module to generate waveform data;

[0029] Described vector waveform generation module: generate the vector waveform for measuring DUT function according to cycle, edge positioning information;

[0030] The switch data ge...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com