Netlist simulation verification method and device

A technology of simulation verification and netlist, applied in design optimization/simulation, special data processing applications, instruments, etc., can solve problems such as project delay, slow netlist simulation process, loss of function development iterations, etc., to speed up and save manpower cost, work efficiency improvement effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

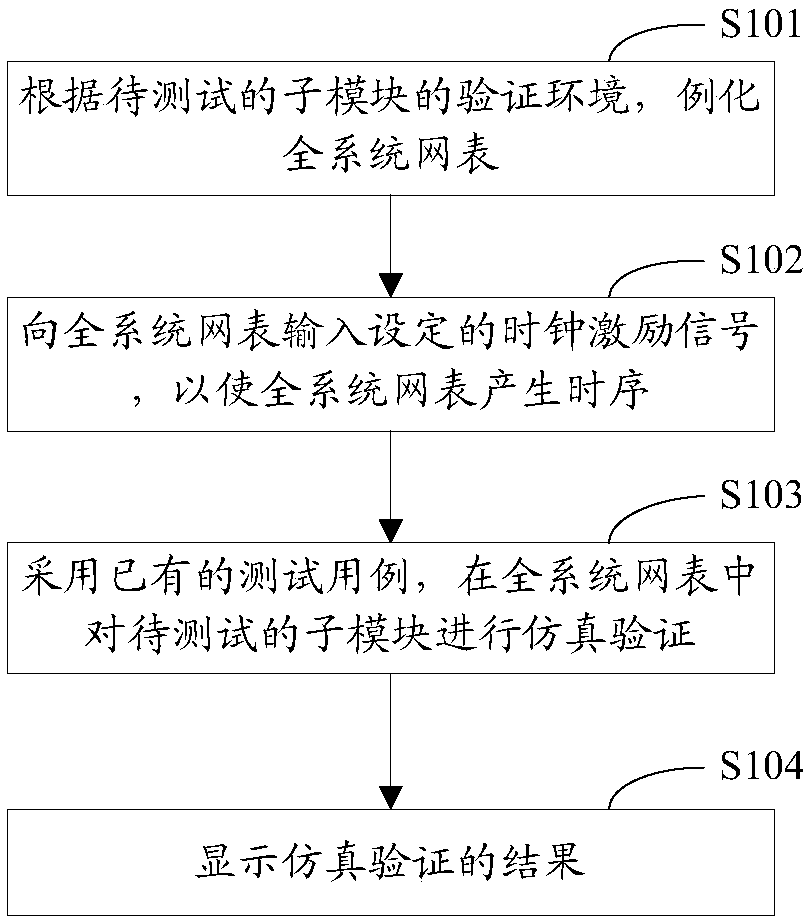

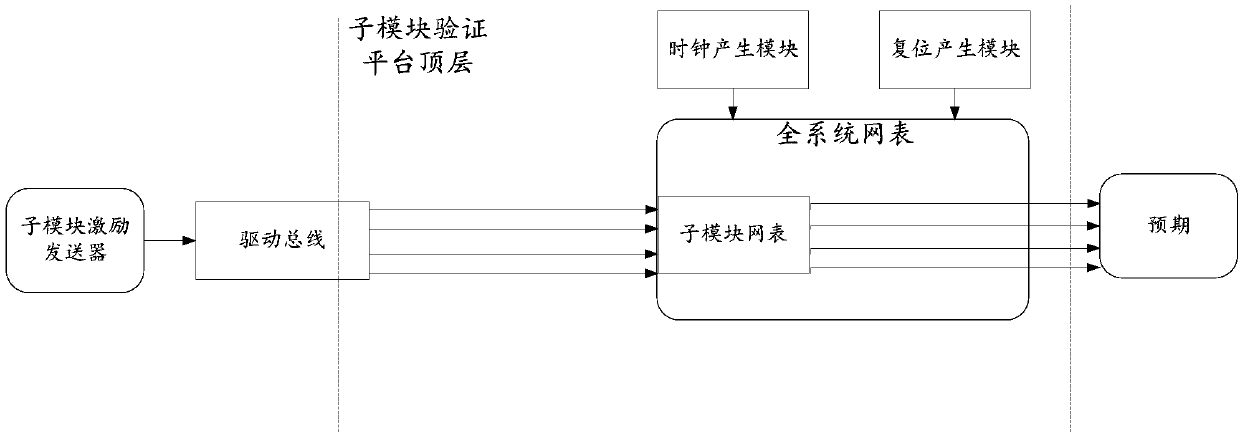

[0054] This embodiment provides a netlist simulation verification method, such as figure 1 with figure 2 As shown, the method includes the following steps:

[0055] Step S101, according to the verification environment of the sub-module to be tested, instantiate the netlist of the whole system.

[0056] When testing a sub-module split in the pre-simulation stage, the verification environment of the sub-module is used to instantiate the netlist of the whole system. For example, when using C language to design an integrated circuit verification program, the class model of the sub-module can be used to define the parameters of the netlist of the whole system.

[0057] Step S102, inputting a set clock excitation signal to the system-wide netlist, so that the system-wide netlist generates timing.

[0058] Before entering the netlist simulation stage, the clock tree is inserted into the system-wide netlist during the netlist synthesis process and place-and-route process. Clock s...

Embodiment 2

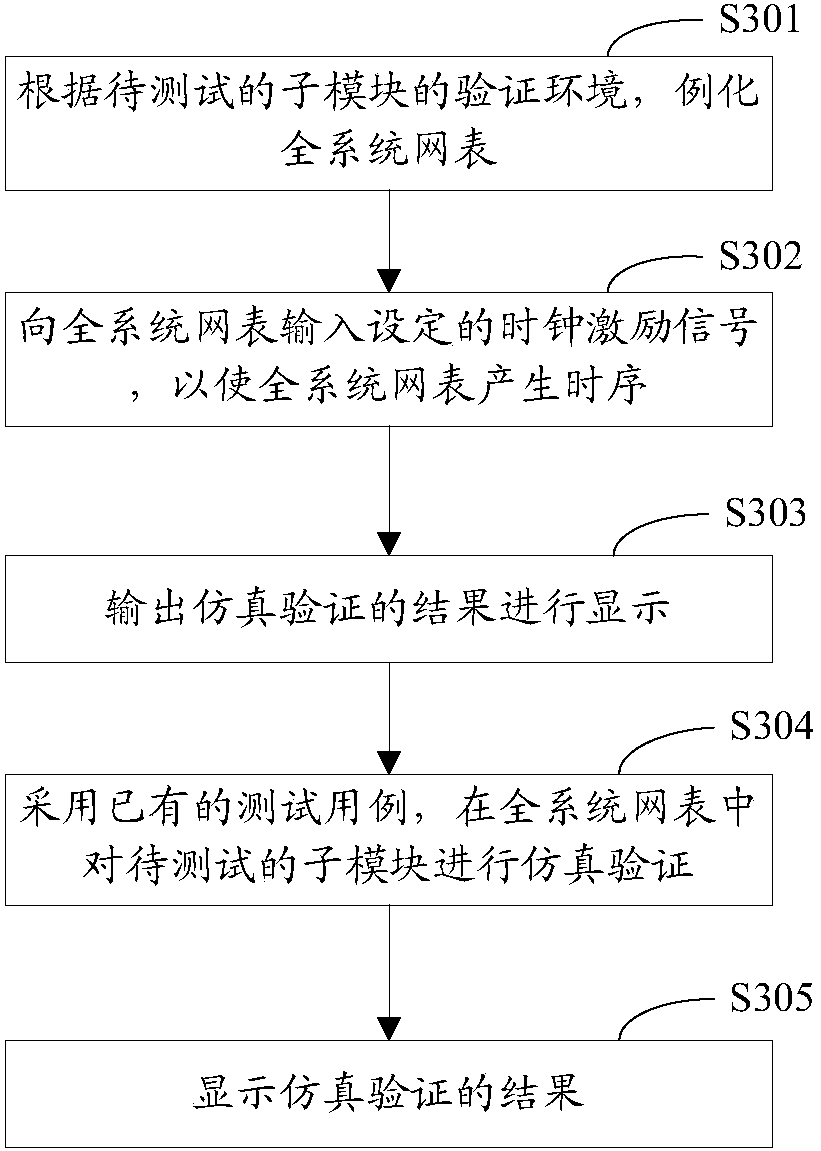

[0065] This embodiment provides a more preferred netlist simulation verification method, such as image 3 As shown, the method includes the following steps:

[0066] Step S301, according to the verification environment of the sub-module to be tested, instantiate the netlist of the whole system.

[0067] Step S302, inputting a set clock excitation signal to the system-wide netlist, so that the system-wide netlist generates timing.

[0068] Step S303, eliminating asynchronous paths that do not meet the timing.

[0069] Because the netlist verification tool will report an error for the path that does not meet the timing, and output an indeterminate state at the Q terminal of the D flip-flop. However, the asynchronous path does not meet the inspection of the setup time and hold time, so the asynchronous path needs to be eliminated. A specific method may be: generating all asynchronous paths in the netlist of the whole system through an asynchronous path search script; taking al...

Embodiment 3

[0077] This embodiment provides a netlist simulation verification device corresponding to the above method embodiment, such as Figure 4 As shown, the device includes:

[0078] The environment building module 41 is used for instantiating the netlist of the whole system according to the verification environment of the sub-module to be tested;

[0079] The clock excitation module 42 is used to input the set clock excitation signal to the netlist of the whole system, so that the netlist of the whole system can generate timing;

[0080] The simulation verification module 43 is used to adopt the existing test case to carry out the simulation verification of the sub-module to be tested in the netlist of the whole system;

[0081] The display module 44 is used for displaying the result of simulation verification.

[0082] Wherein, the environment establishment module 41 is also used to instantiate the netlist of the whole system using the verification environment of the sub-modules...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com