Optimization method for temperature cyclic stress acceleration model of semiconductor device

A cyclic stress and acceleration model technology, which is applied in instruments, special data processing applications, electrical digital data processing, etc., can solve the problem of inability to quickly and accurately select the temperature cyclic stress acceleration model, and achieve the effect of solving irrationality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

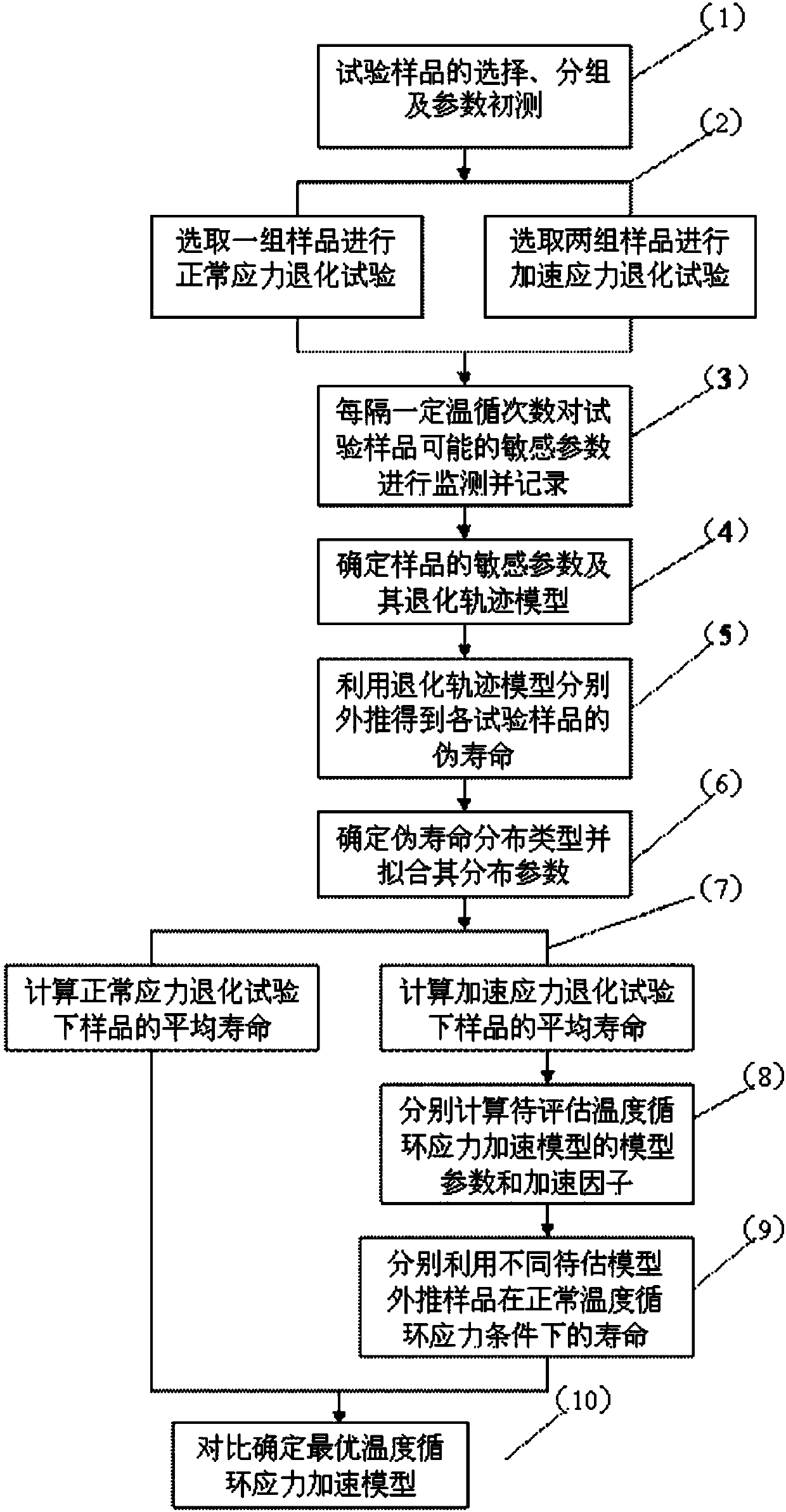

[0032] The preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0033] figure 1 It is a flow chart of the preferred method for the temperature cycle stress acceleration model of the semiconductor device of the present invention. Such as figure 1 As shown, the steps of the method for optimizing the temperature cycle stress acceleration model of a semiconductor device according to an embodiment of the present invention include:

[0034] Step (1): Randomly select ≥150 circuit samples from the qualified semiconductor devices, number each device sample, conduct a full-parameter test on each device sample according to the detailed product specification, and record all the circuit samples of the tested device sample. Parameter value, randomly divided into 3 groups (each group ≥ 50);

[0035] Step (2): Randomly select one group of device samples, and conduct a degradation test under normal temperature cycle ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com