Power semiconductor device loss characteristic test platform and method

A technology for power semiconductors and test platforms, applied in instruments, measuring devices, measuring electrical variables, etc., can solve the problems of difficult adjustment of load current, inconsistent device working states, and small number of measurable devices, and achieve accurate switching loss test results, Realize the effect of cycle test and good loss test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] The present invention will be described in detail below in conjunction with specific embodiments. The following examples will help those skilled in the art to further understand the present invention, but do not limit the present invention in any form. It should be noted that those skilled in the art can make several changes and improvements without departing from the concept of the present invention. These all belong to the protection scope of the present invention.

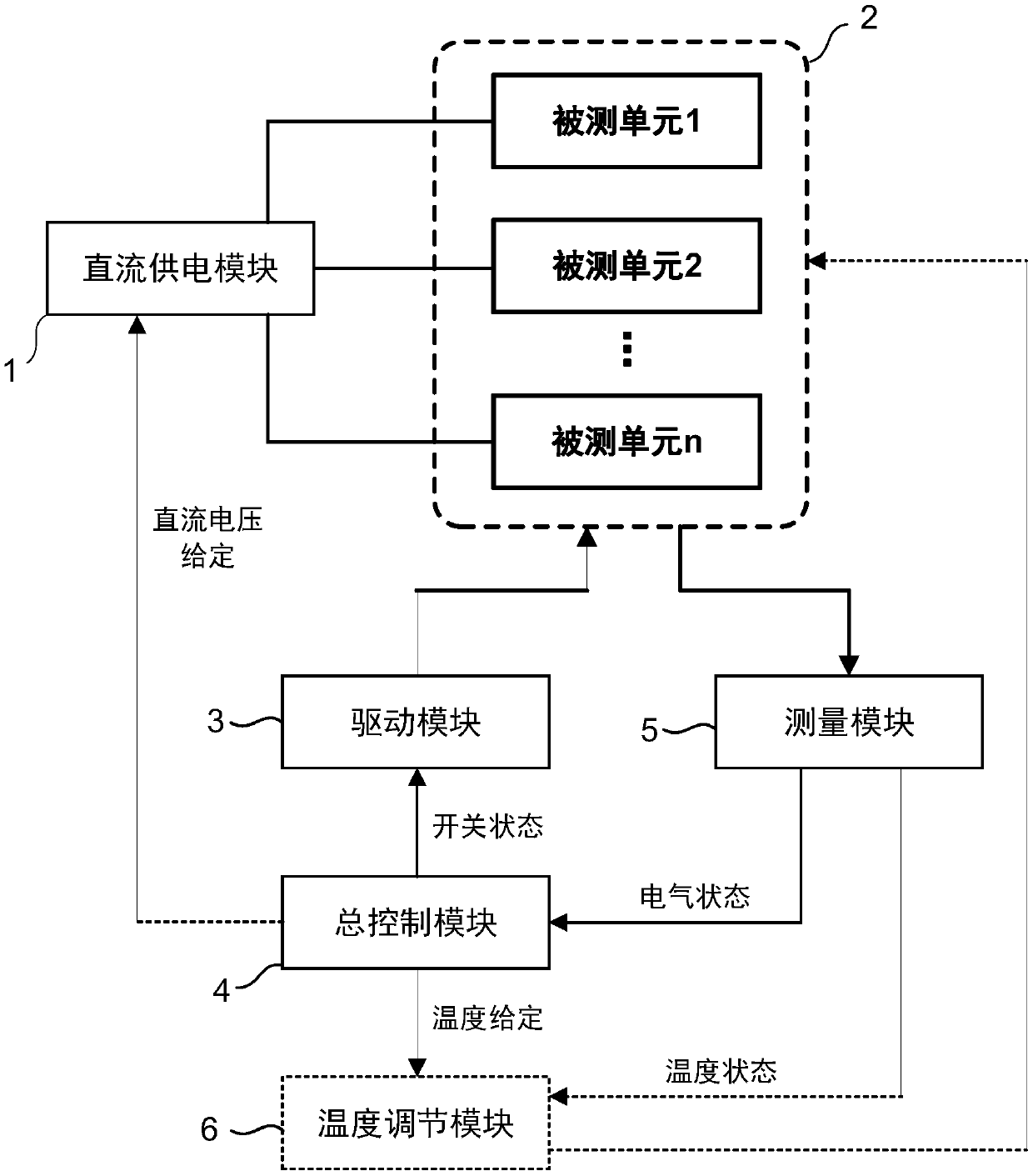

[0066] figure 1 The structure schematic diagram of the test platform of the power semiconductor device loss characteristic provided for the present invention, according to figure 1 As shown, it may include: a DC power supply module 1 , a module under test 2 including at least one unit under test, a drive module 3 , a measurement module 5 , a general control module 4 , or a temperature adjustment module 6 . Wherein, the number of DC output port groups of the DC power supply module 1 is the same as the n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com