A silicon carbide trench MOS device and manufacturing method thereof

A technology of MOS devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as high production costs, high power loss, and low work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

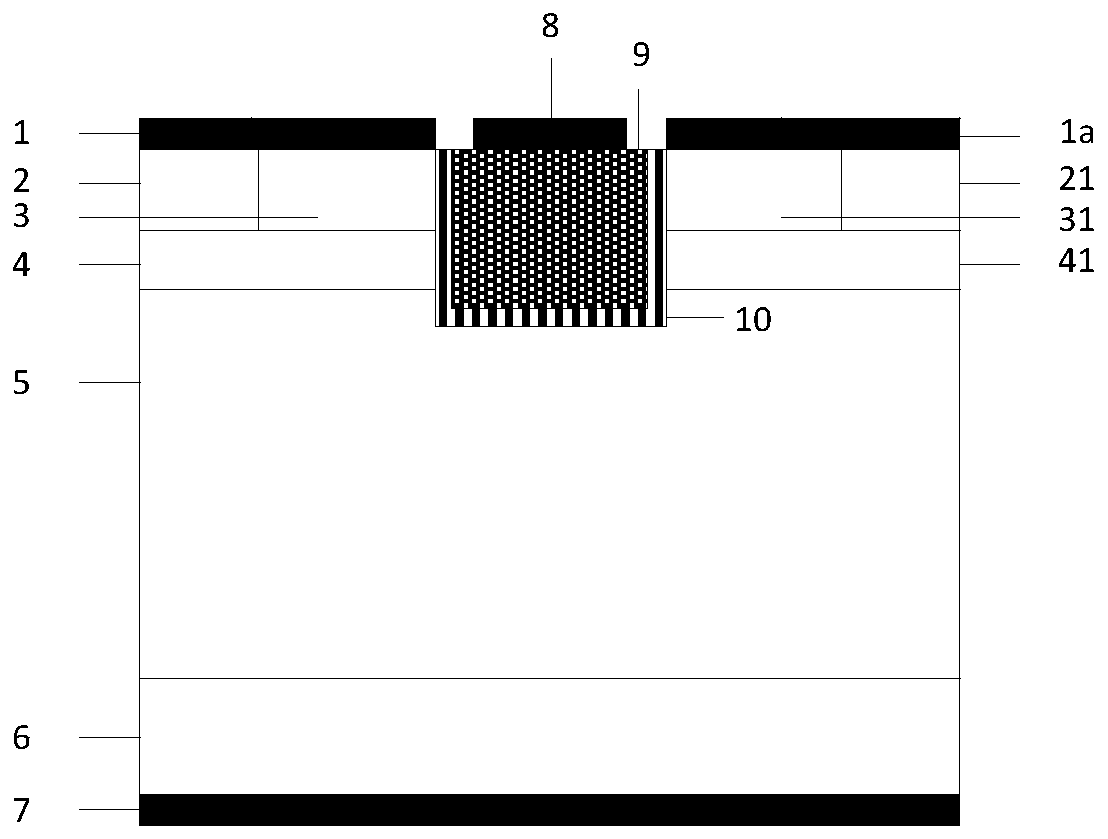

[0109] A silicon carbide Trench MOS device, its cell structure is as follows figure 2 Shown includes: metal drain electrodes 7, N + Substrate 6 and N - epitaxial layer 5; the N - One end of the upper layer of the epitaxial layer 5 has a first Pbase region 4, the N - The other end of the upper layer of the epitaxial layer 5 has a second Pbase region 41; the first Pbase region 4 has mutually independent first N + source region 3 and the first P + Contact region 2; the second Pbase region 41 has second N independent of each other + source region 31 and the second P + Contact area 21; the first P + contact zone 2 and the first N + The upper surface of the source region 3 has a first metal source electrode 1; the second P + contact region 21 and the second N + The upper surface of the source region 31 has a second metal source electrode 1a; it is characterized in that: there is a P-type polysilicon region 11 with a π-type distribution in the N-epitaxial layer 5 below the m...

Embodiment 2

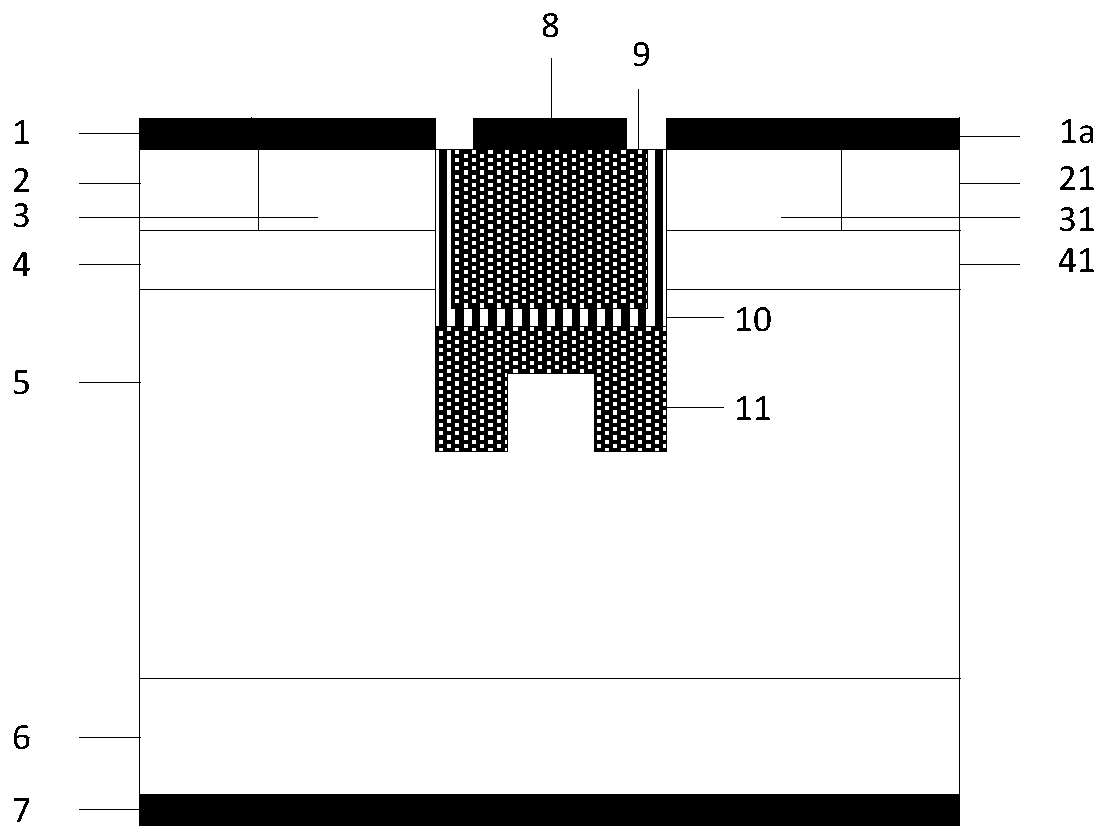

[0112] In this embodiment, independent first P + SiC region 12 and the second P + Except for the silicon carbide region 121, all the other structures are the same as in Embodiment 1, such as image 3 Shown; the first P in this embodiment + SiC region 12 and the second P + The width of the silicon carbide region 121 is the same as that of the corresponding branch region, and the width is 0.1-0.3 μm.

[0113] Compared with Example 1, the two P introduced in this example + The silicon carbide regions 12 and 121 can shield the P-type polysilicon region 11 and the trench gate thereon from the electric field, improve the withstand voltage of the device, and reduce the reverse leakage current.

Embodiment 3

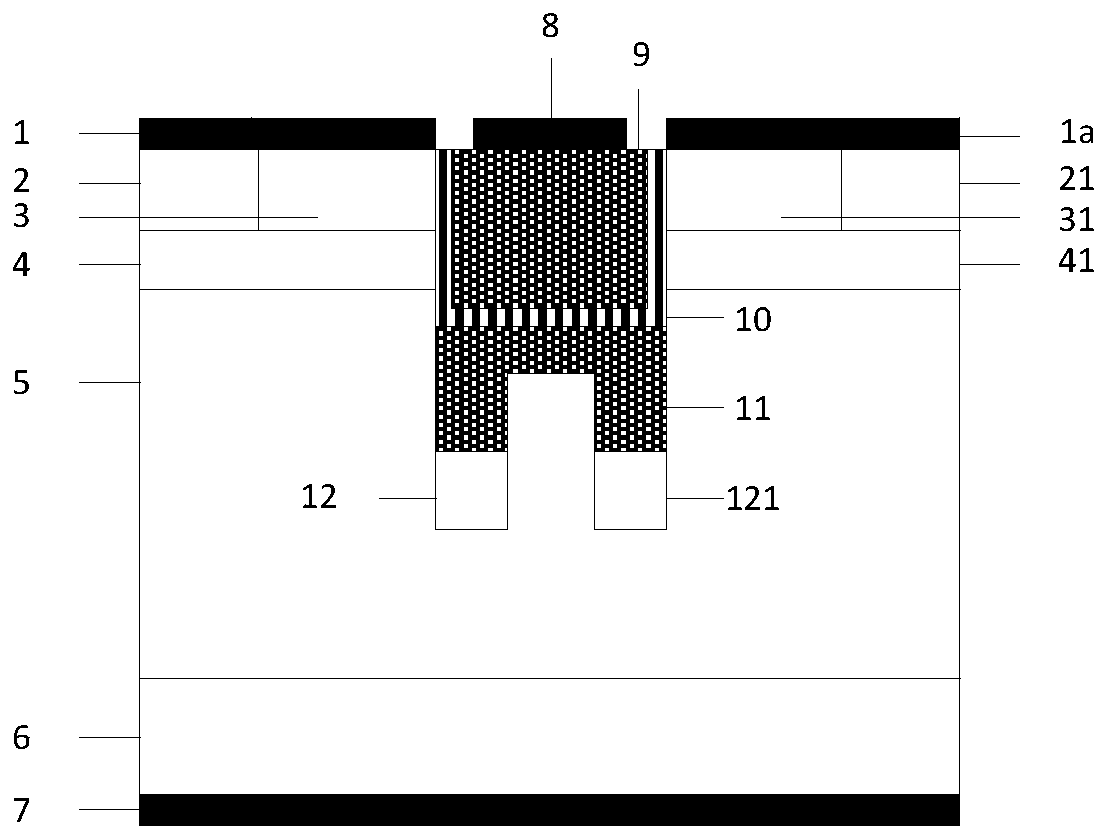

[0115] In addition to making the first P + SiC region 12 and the second P + Except that the width of the silicon carbide region 121 is greater than the width of the corresponding branch region of the P-type polysilicon region 11 in the π-type distribution, the rest of the structure is the same as that of Embodiment 2, as Figure 4 shown.

[0116] In this example, the first P + SiC region 12 and the second P + The width of the silicon carbide region 121 is 0.1-0.4 μm.

[0117] This implementation will P + The larger lateral dimensions of the silicon carbide regions 12 and 121 can enable the P-type polysilicon region 11 to have a stronger electric field shielding effect, further improve the withstand voltage capability of the device, and reduce the reverse leakage current.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com