Array substrate, manufacturing method thereof, and display device

A technology for an array substrate and a manufacturing method, which is applied in the fields of array substrates and their manufacturing methods and display devices, and can solve problems such as difficulty in detecting line defects, short-circuiting of data lines, and decline in product yield, so as to reduce the probability of occurrence of line defects , to ensure the display effect and improve the yield rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order for those skilled in the art to better understand the technical solution of the present invention, the array substrate, its manufacturing method and display device provided by the present invention will be described in detail below with reference to the accompanying drawings.

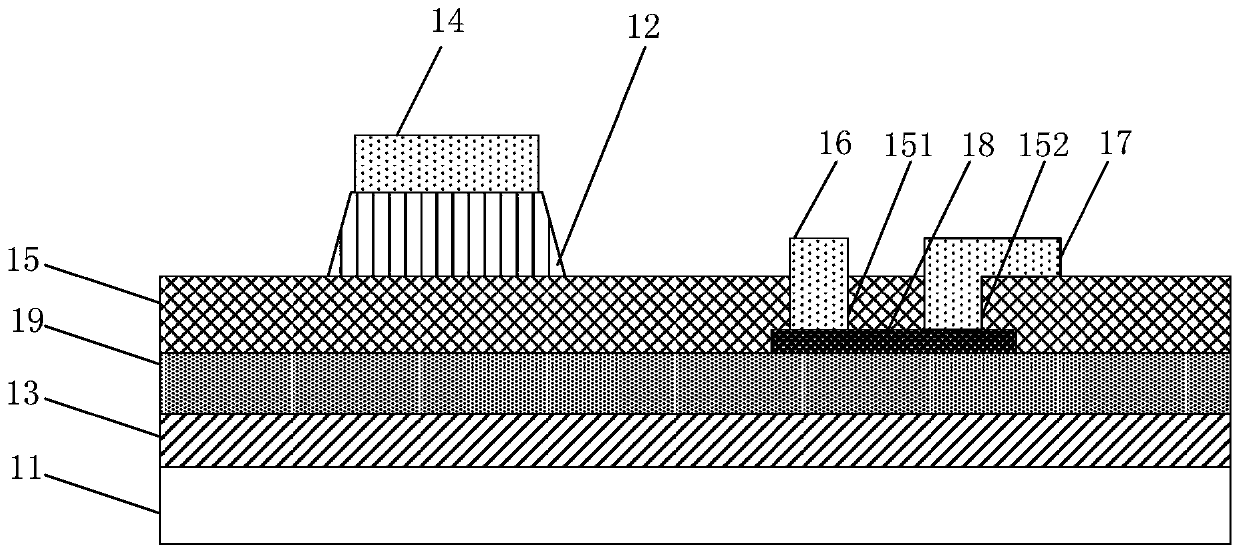

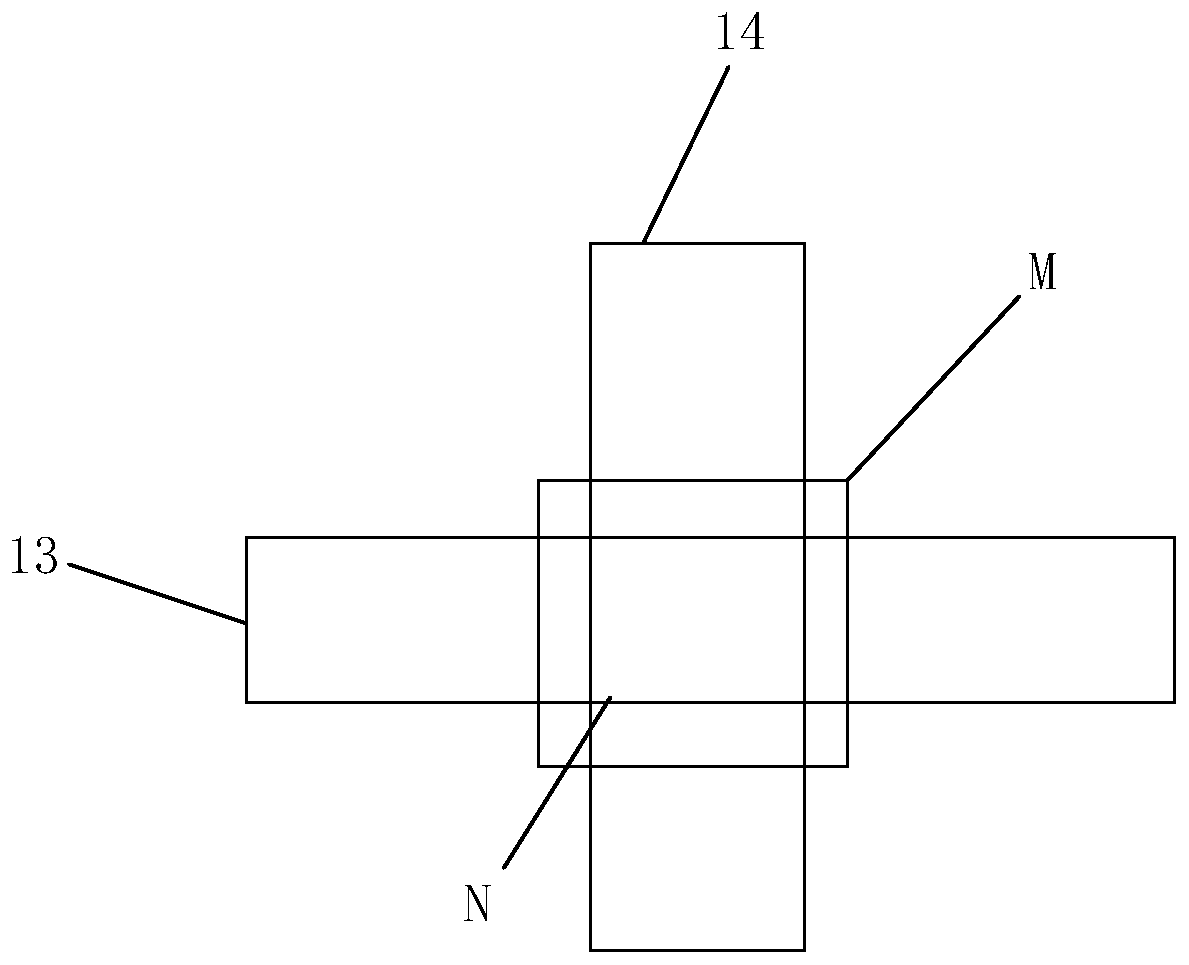

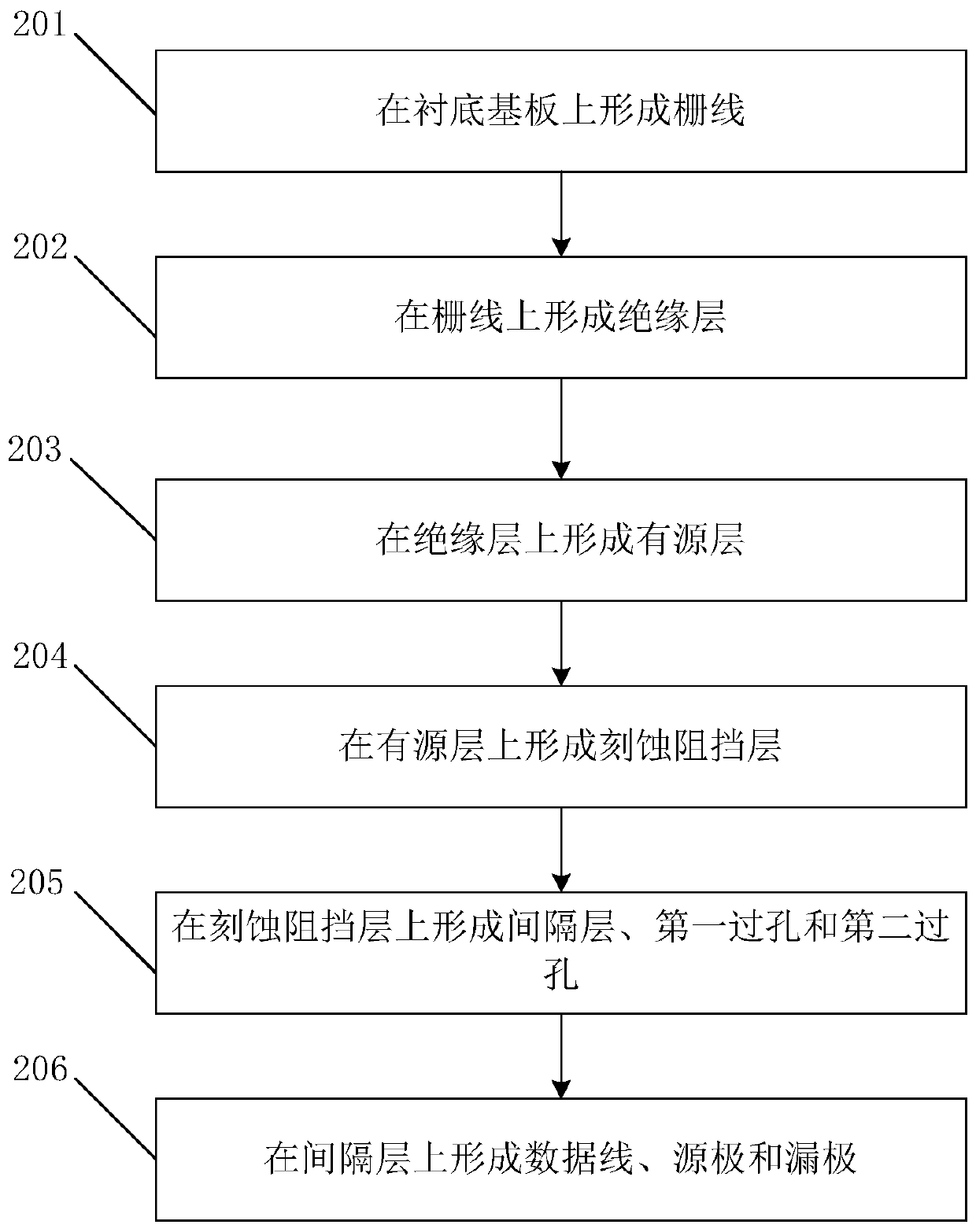

[0041] figure 1 It is a schematic structural diagram of an array substrate provided in Embodiment 1 of the present invention, figure 2 It is the top view of the middle spacer layer, the first conductive pattern layer and the second conductive pattern layer in embodiment one, as figure 1 and figure 2 As shown, the array substrate includes a base substrate 11 and a spacer layer 12 located on the base substrate 11, a first conductive pattern layer and a second conductive pattern layer, and the spacer layer 12 is arranged on the first conductive pattern layer and the second conductive pattern layer between the layers, and the projection M of the spacer layer 12 on the substrate 11 covers...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com