Parallel bus automatic compensation method based on FPGA

An automatic compensation and bus technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve problems such as signal asynchronous, unreliable data transmission, signal failure, etc., to ensure reliable sampling, solve signal asynchronous phenomena, and avoid bit errors high rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

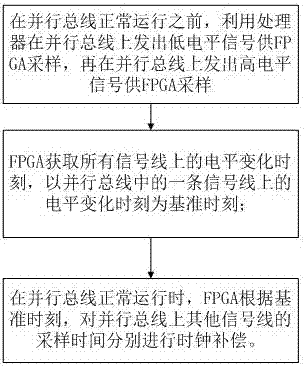

[0026] The present invention provides a kind of parallel bus automatic compensation method based on FPGA:

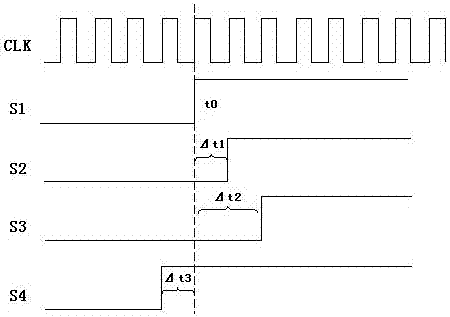

[0027] Among them, before the normal operation of the parallel bus, the processor is used to send a low-level signal on the parallel bus for FPGA sampling, and then a high-level signal is sent on the parallel bus for FPGA sampling;

[0028] The FPGA obtains the level change moment of all signal lines, and takes the level change moment of one signal line in the parallel bus as the reference time;

[0029] When the parallel bus is running normally, the FPGA performs clock compensation for the sampling time of other signal lines on the parallel bus according to the reference time.

[0030] At the same time, it provides an FPGA-based parallel bus automatic compensation system, including FPGA modules, processors,

[0031] Wherein, before the normal operation of the parallel bus, the processor is used to send a low-level signal on the parallel bus for the FPGA module to sampl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com