A level conversion circuit and method

A technology for converting circuits and levels, applied in logic circuits, eliminating voltage/current interference, logic circuit connection/interface layout, etc., can solve the problems of many burrs, consumption, and difficulty in controlling the level of the subsequent circuit of the output voltage signal.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

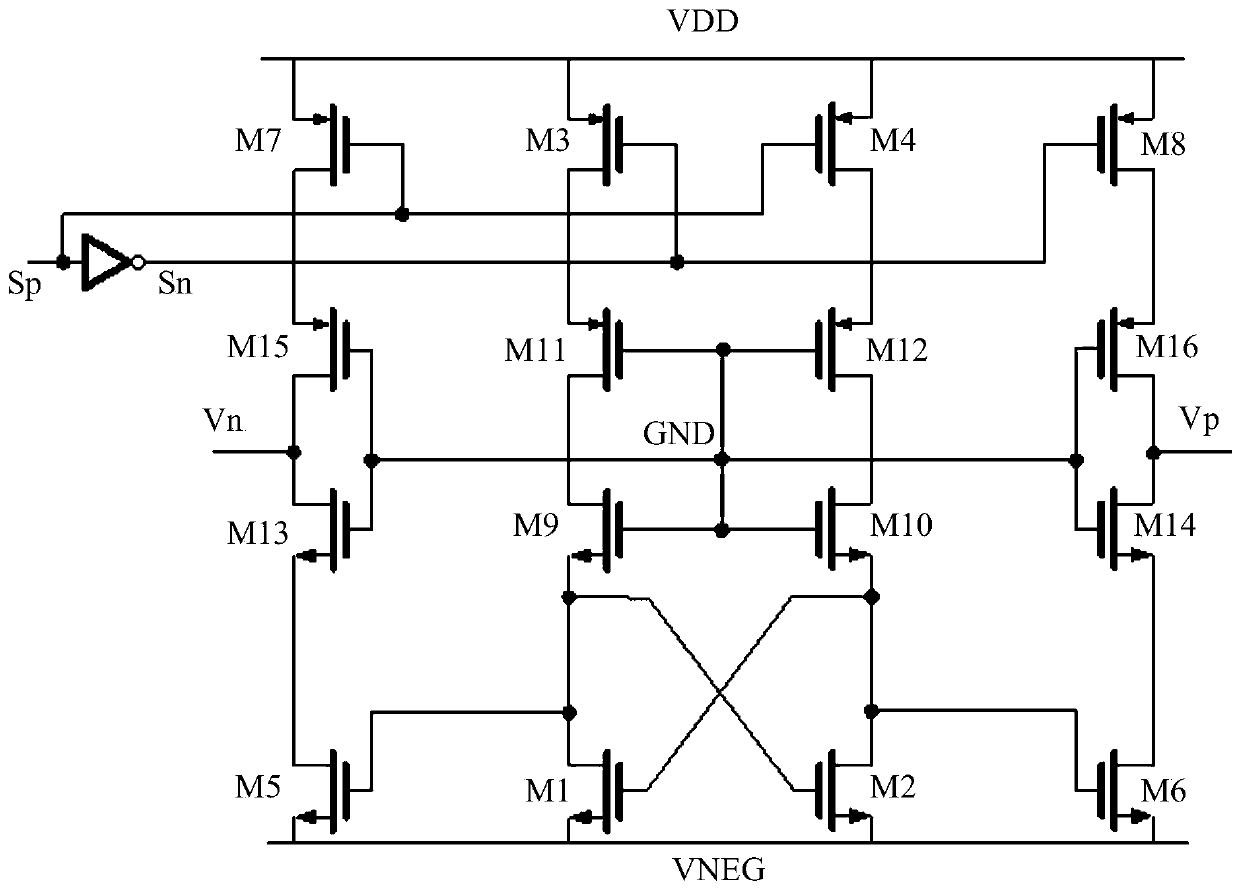

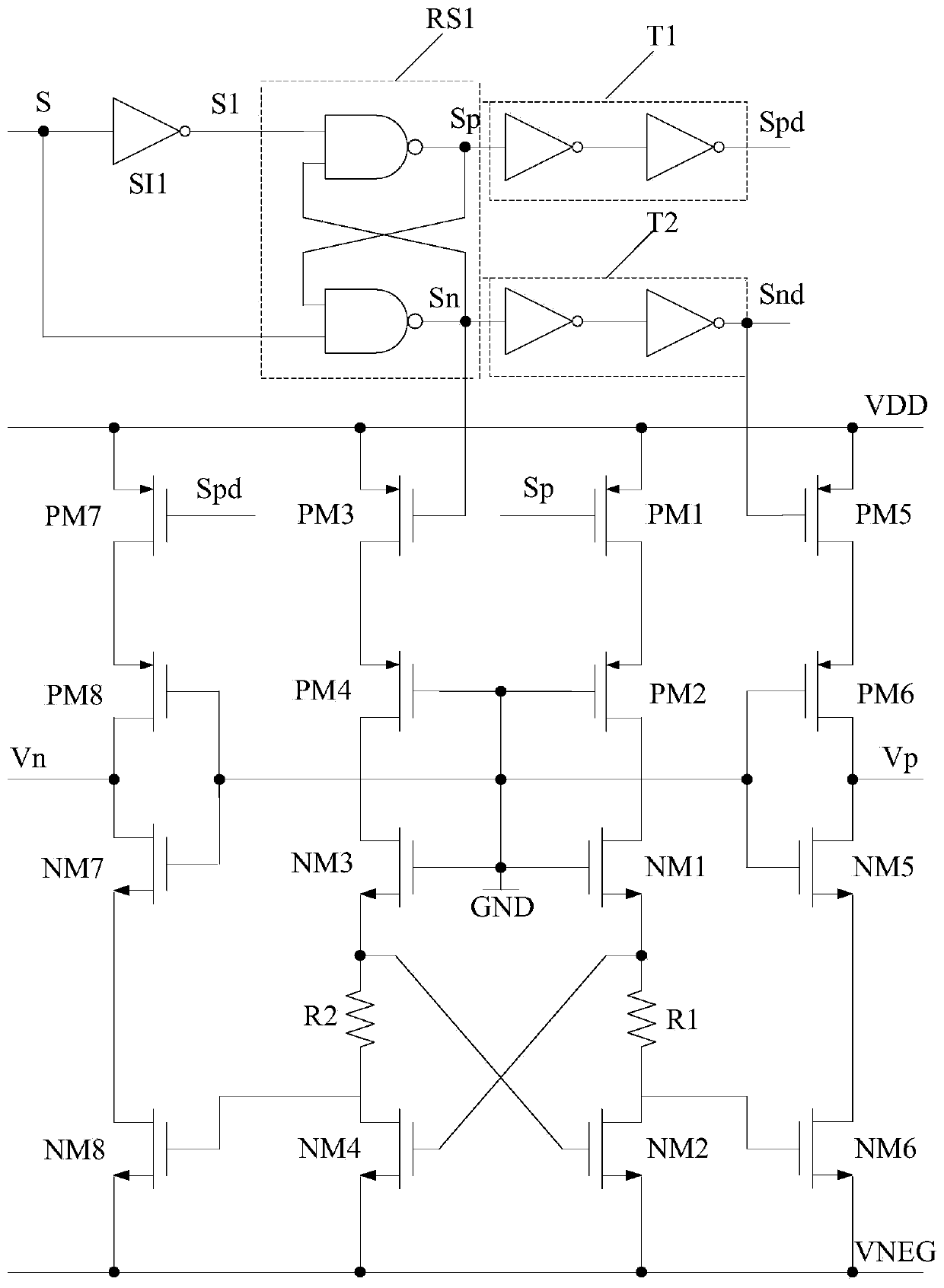

[0061] The level conversion circuit provided by the embodiment of the present invention is mainly used in the design of integrated circuits. By adjusting the timing of the level signal, it is avoided that the positive power supply VDD and the negative power supply VNEG are turned on simultaneously due to the simultaneous conduction of the PMOS transistor and the NMOS transistor. The leakage caused by the loop can significantly reduce the dynamic current and reduce the edge glitch of the output voltage signal.

[0062] The realization of the purpose of the present invention, functional characteristics and advantages will be further described in conjunction with the embodiments and with reference to the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

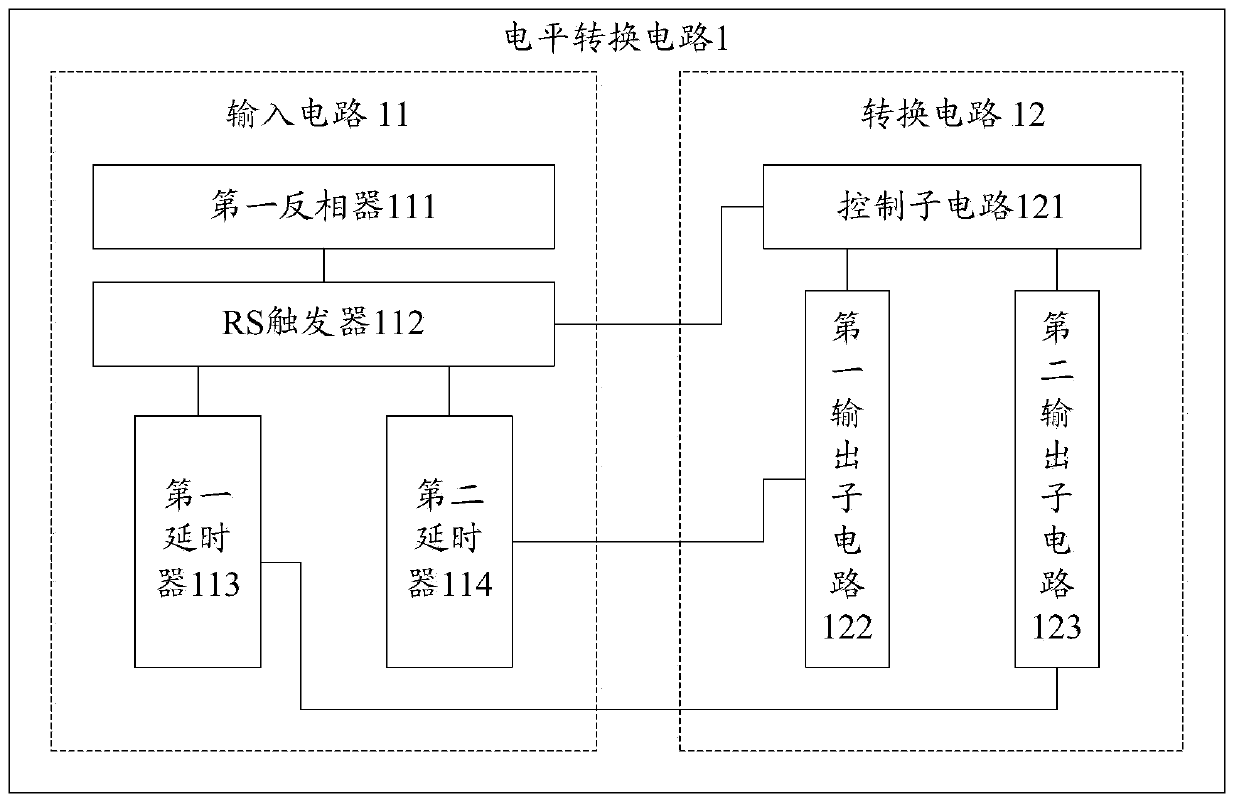

[0063] figure 2 It is a schematic block diagram of the first embodiment of the level conversion circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com