Method for improving chip verification coverage rate based on tree backtracking algorithm

A backtracking algorithm and coverage technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as analysis errors, time-consuming, and increased workload, and achieve the effect of improving verification efficiency and speeding up the convergence process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In view of the deficiencies in the prior art, the inventor of this case was able to propose the technical solution of the present invention after long-term research and extensive practice. The technical solution, its implementation process and principle will be further explained as follows.

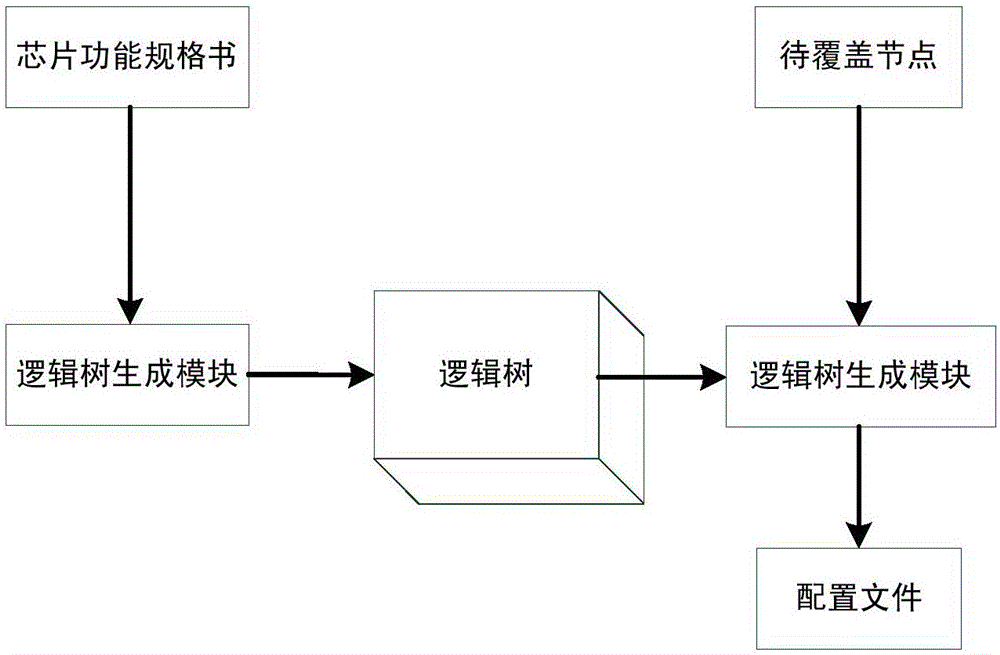

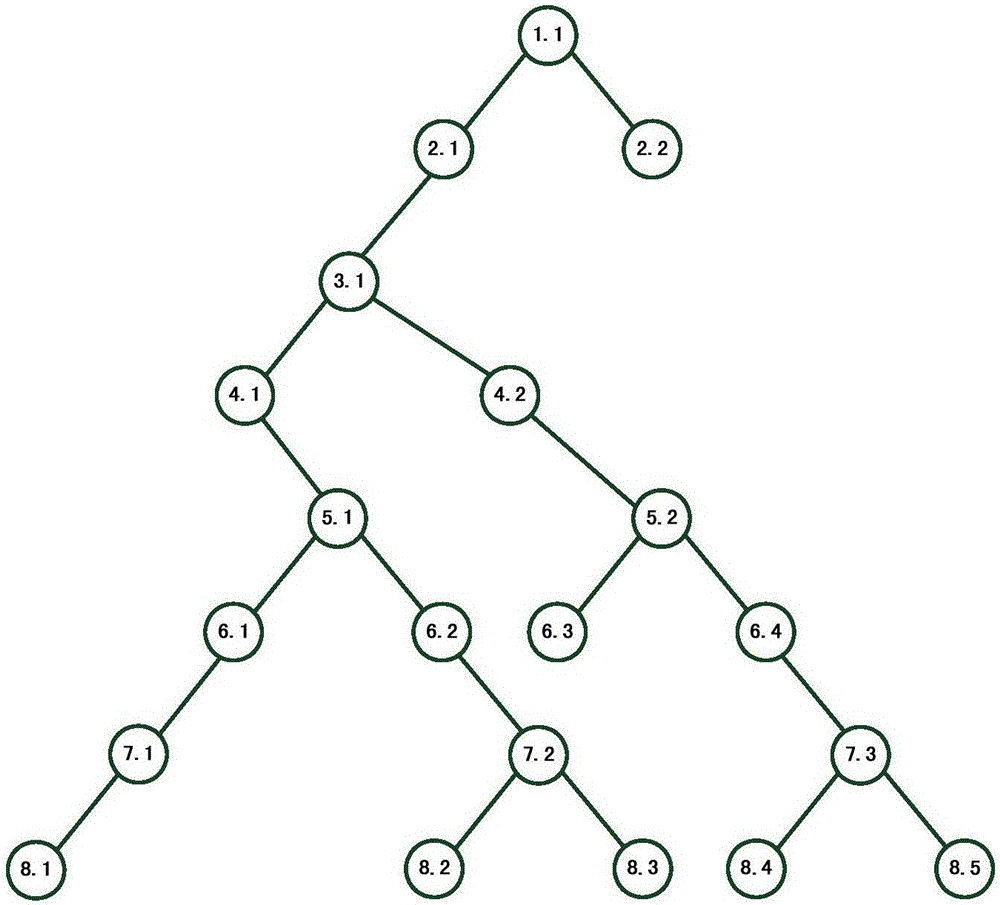

[0018] The invention proposes a method for improving chip verification coverage based on a tree backtracking algorithm. A logic tree is generated according to the functions realized by the chip, and each point to be covered is a node on the logic tree. The path information from the root node to a point to be covered is obtained through the tree backtracking algorithm, and thus the configuration information covering the point is obtained. According to the configuration information, the corresponding constraint stimulus can be generated for the point to be covered, so as to realize the chip verification of the function. By adopting the method proposed in the embodiment of the presen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com