Digital Calibration Method for Analog-to-Digital Converter of High Performance CMOS Image Sensor Array

A technology of image sensor and analog-to-digital converter, which is applied in the direction of image communication, color TV parts, TV system parts, etc., to achieve the effect of saving chip area, reducing mismatching problems, and good dynamic performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

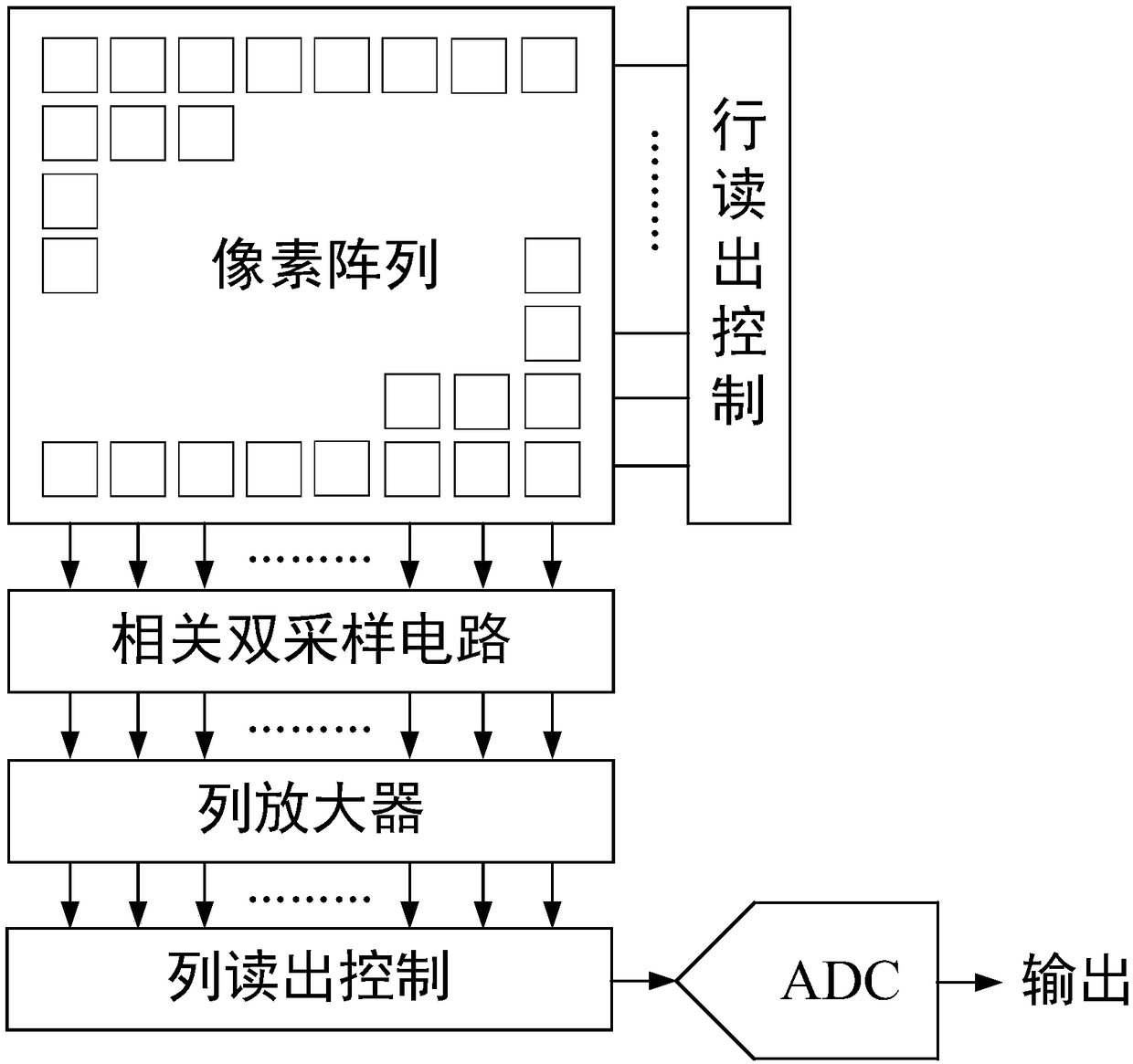

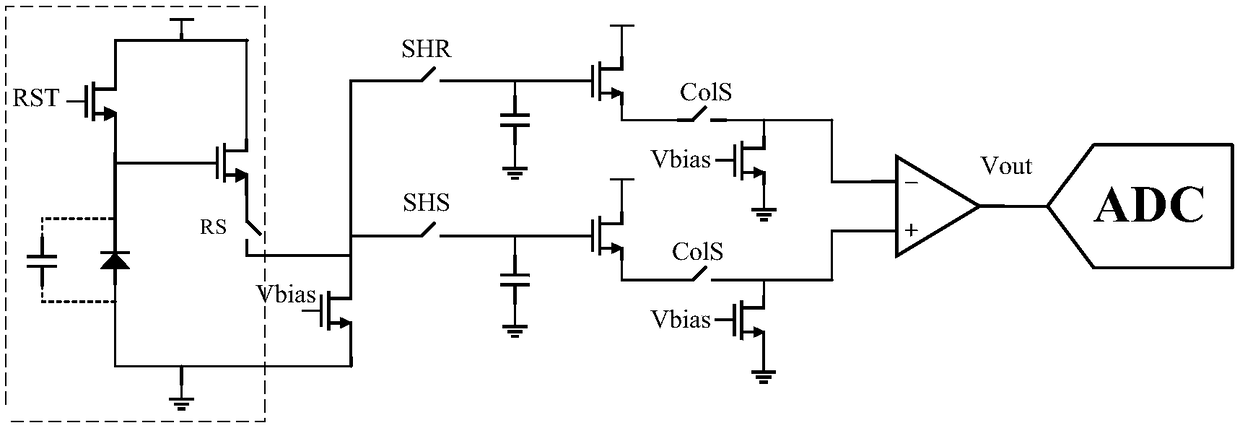

Method used

Image

Examples

Embodiment 1

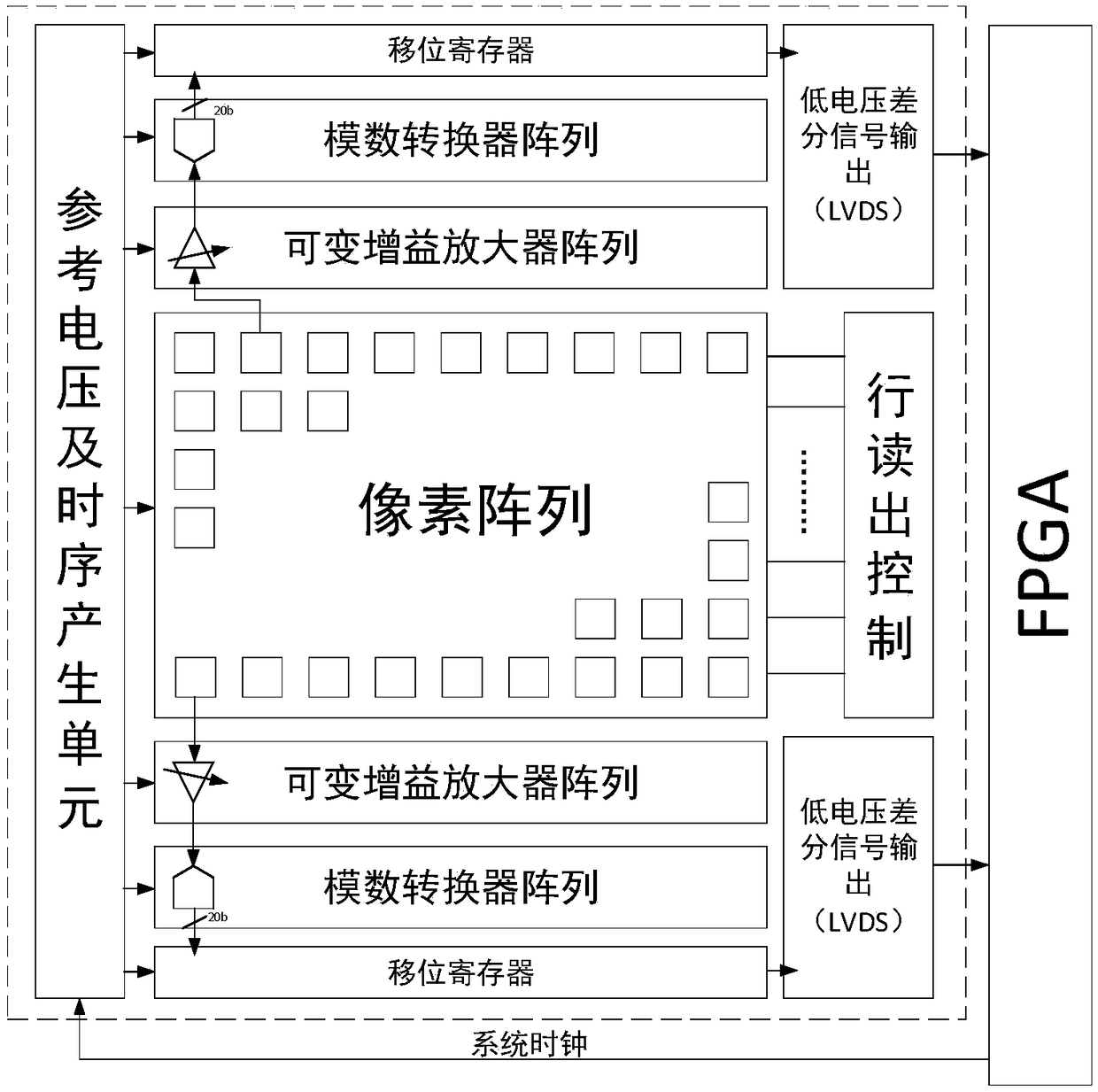

[0042] The digital calibration method of the high-performance CMOS image sensor array analog-to-digital converter, the specific process is as follows: N-way ADCs on the CIS chip are arranged in an array, and during normal operation, the data strobe (MUX) connects the sensor output to the ADC input, In the correction stage, the data strobe connects the correction signal to the ADC input, and the output of the ADC is connected to the in-system programming (ISP) chip outside the CIS chip through a low-voltage differential signal output (LVDS) high-speed interface. During the digital correction process, the ADC The output first passes through the bit weight adjustment circuit for data recovery operation, and then input to the digital correction engine for correction operation, feedback correction data to the bit weight adjustment circuit for bit weight correction, and then outputs the corrected data to the subsequent image signal processing module The circuit completes the followin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com