Single-event reinforced FPGA configuration circuit with code stream error detection and error correction function

A single-particle reinforcement and configuration circuit technology, applied in the direction of using linear codes for error correction/detection, using block codes for error correction/detection, single error correction, etc., can solve interconnection line short circuit or open circuit, partial circuit function error, Circuit failure and other problems, to achieve the effect of strong flexibility and good application value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Aiming at the deficiencies of the prior art, the present invention overcomes the defects that the traditional FPGA configuration circuit can only detect errors generated during code stream transmission, cannot locate errors, and cannot correct errors, and proposes a The configuration circuit of the single particle reinforced FPGA with the error detection function will be described in detail below in conjunction with the accompanying drawings.

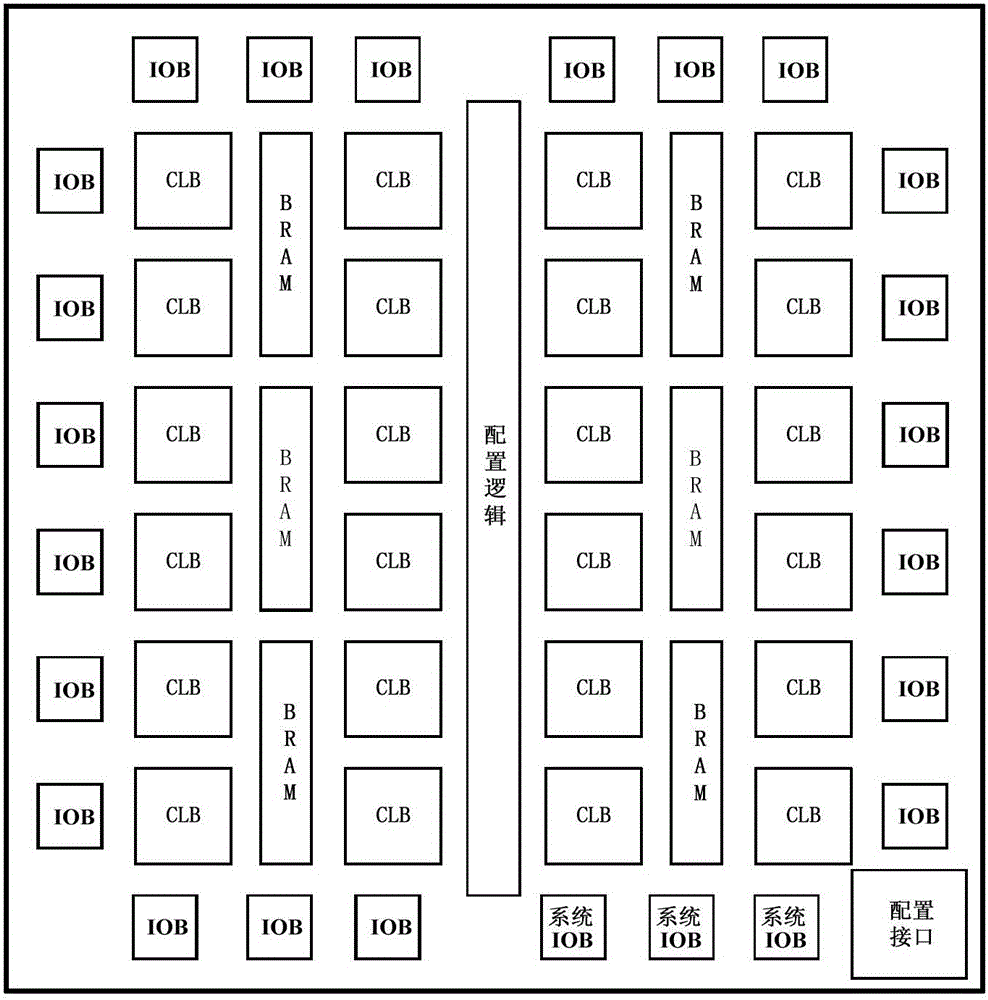

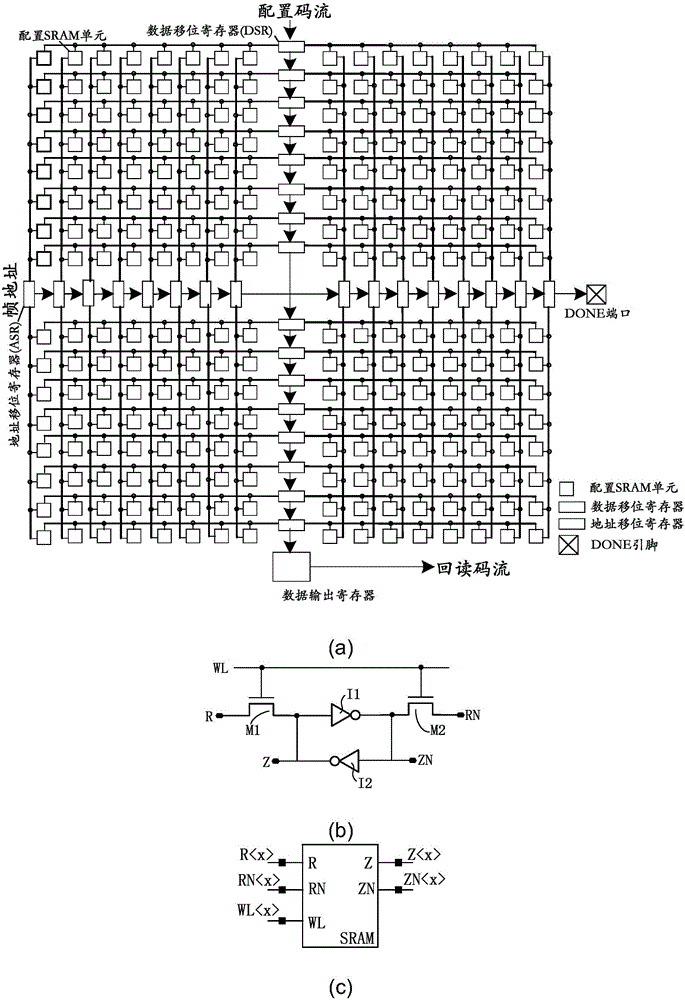

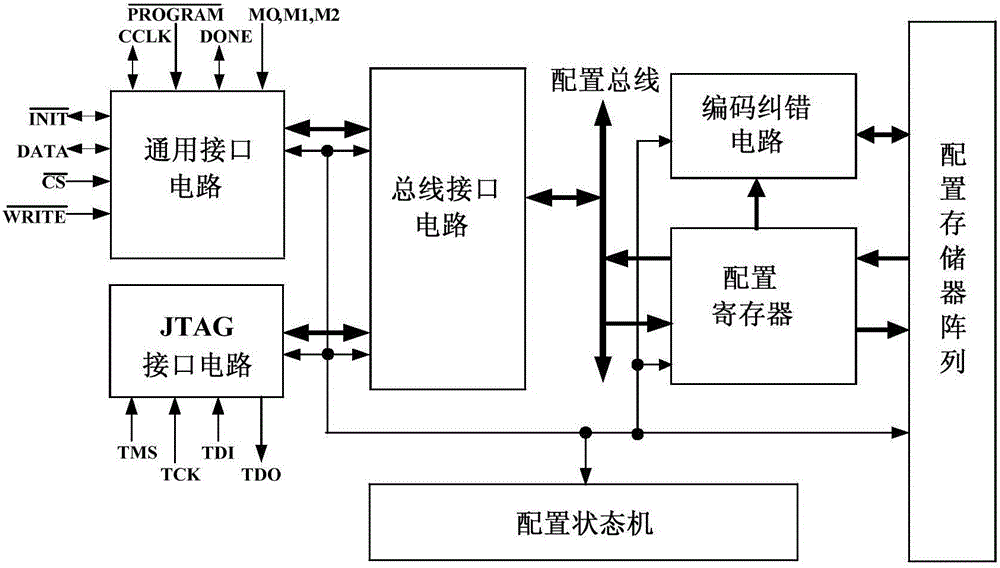

[0026] Such as image 3 As shown, the configuration circuit of the present invention includes a general interface circuit, a JTAG interface circuit, a bus interface circuit, a configuration bus, a configuration register, an encoding error correction circuit, a configuration state machine, and a configuration memory array, wherein the bus interface circuit is connected to the configuration bus, one or A plurality of external communication interface circuits (including JTAG interface circuit, general interface circuit), a plurality...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com