Low-offset operational amplifier

An operational amplifier and amplifying circuit technology, applied in amplifiers, amplifier combinations, differential amplifiers, etc., can solve problems such as reducing the gain of operational amplifiers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

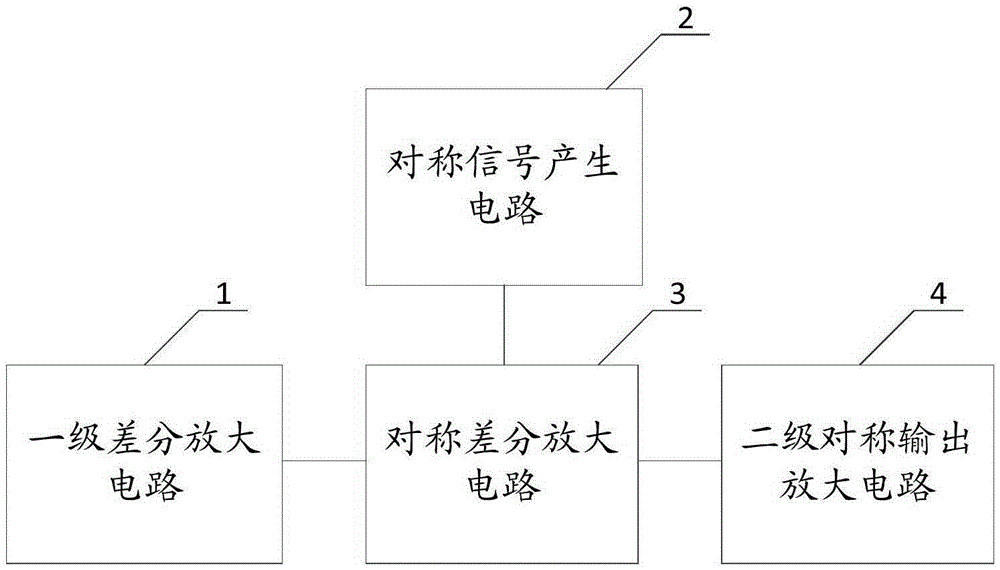

[0027] Please refer to figure 1 , figure 1 A structural schematic diagram of a low offset operational amplifier provided by the present invention, the low offset operational amplifier includes:

[0028] A first-stage differential amplifier circuit 1, a symmetrical differential amplifier circuit 3, a symmetrical signal generating circuit 2, and a second-stage symmetrical output amplifier circuit 4, wherein:

[0029] The output end of the first-stage differential amplifier circuit 1 is connected to the first input end of the symmetrical differential amplifier circuit 3, and the first-stage differential amplifier circuit 1 is used to amplify the input signal to obtain a first-stage amplified voltage and output it to the first input end;

[0030] The second input end of the symmetrical differential amplifier circuit 3 is connected to the output end of the symmetrical signal generating circuit 2; wherein, the symmetrical signal generating circuit 2 is used to generate a symmetrica...

Embodiment 2

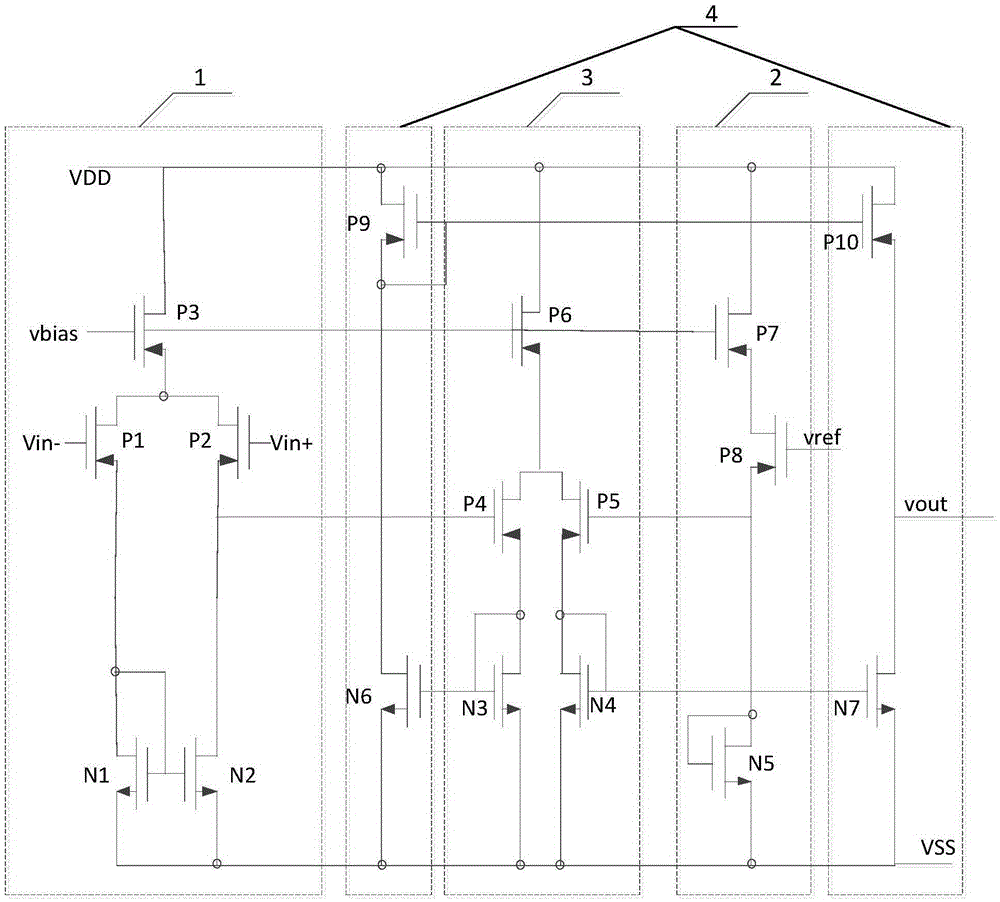

[0037] Please refer to figure 2 , figure 2 A schematic structural diagram of another low-offset operational amplifier provided by the present invention. On the basis of Embodiment 1, the low-offset operational amplifier:

[0038] Preferably, the primary differential amplifier circuit 1 specifically includes a first PMOS, a second PMOS, a third PMOS and an active load circuit, wherein:

[0039] The source of the third PMOS is connected to the power supply, the gate of the third PMOS is connected to the bias voltage, the drain of the third PMOS is respectively connected to the sources of the first PMOS and the second PMOS, and the gate of the first PMOS is connected to the source of the first PMOS. The negative pole of the input signal, the drain of the first PMOS is connected to the first end of the active load circuit, the gate of the second PMOS is connected to the positive pole of the input signal, and the drain of the second PMOS is used as the output terminal of the fir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com