Shift register unit and a drive method, a shift register and a display device thereof

A technology of a shift register and a driving method, which is applied in static memory, digital memory information, instruments, etc., can solve problems such as insufficient opening, reduced display effect of a display device, and uneven display of a display device, so as to achieve uniform display and improve display effect of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

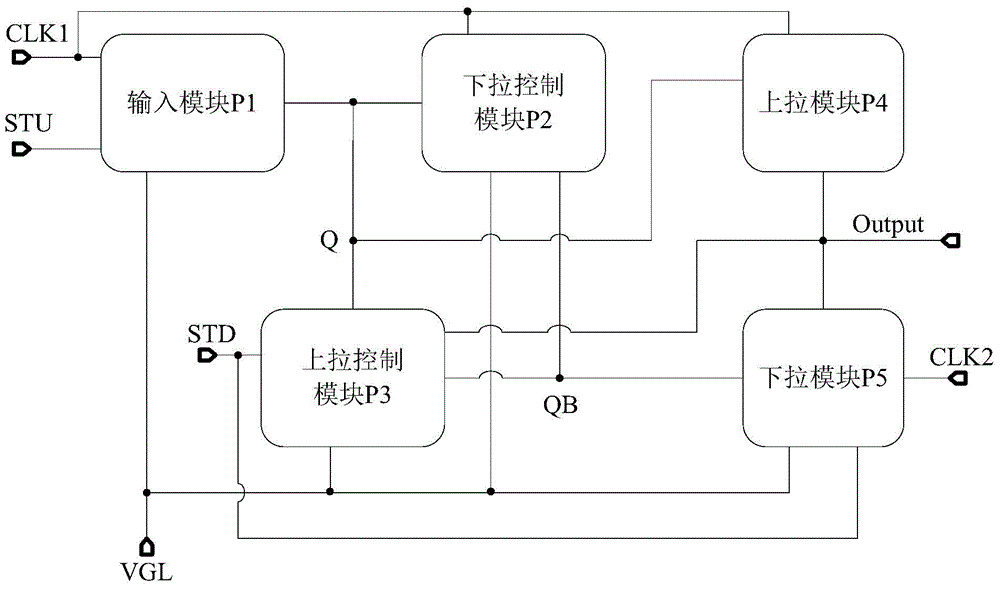

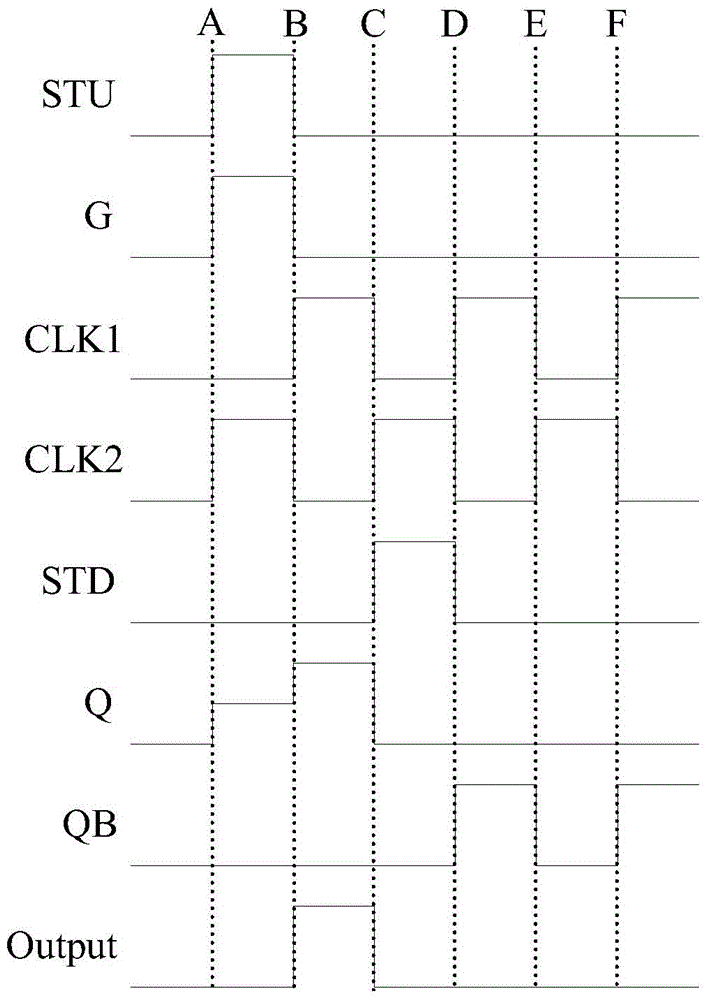

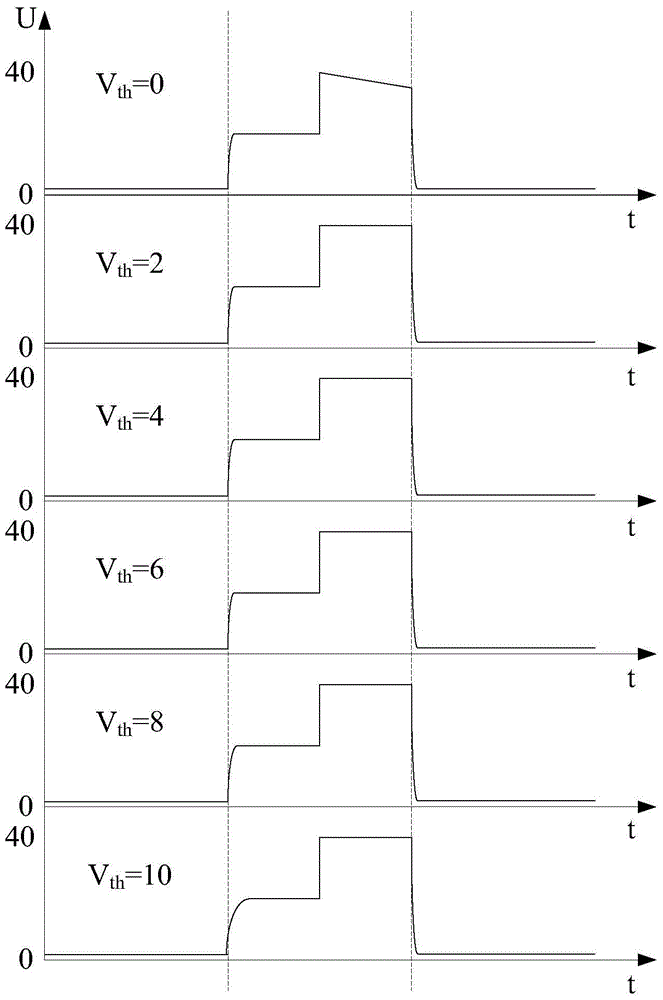

[0028] see figure 1 , The shift register unit provided by the embodiment of the present invention includes an input module P1, a pull-down control module P2, a pull-up control module P3, a pull-up module P4 and a pull-down module P5. Wherein, the input module P1 is connected with the first trigger signal terminal STU, the first clock signal terminal CLK1, the low level terminal VGL and the pull-up control node Q, and the input module P1 is used to utilize the bootstrap effect to convert the first trigger signal terminal STU to Signal without threshold voltage V th The lossy ground is transmitted to the pull-up control node Q, and the voltages of the gate-on signal and the first pole-on signal of the transistor in the input module are both V1 (high level signal), and the gate-off signal and the first pole open signal of the transistor in the input module are The voltage of one pole off signal is V2 (low level signal), and the voltage of the signal transmitted to the pull-up co...

Embodiment 2

[0041] see Figure 4 The specific structures of the input module P1, the pull-down control module P2, the pull-up control module P3, the pull-up module P4 and the pull-down module P5 in the first embodiment will be described in detail below.

[0042] The input module P1 includes a first transistor T1, a second transistor T2, a third transistor T3, and a first capacitor C1; wherein, the gate of the first transistor T1 is connected to the first trigger signal terminal STU, and its first pole is connected to the second The second pole of the transistor T2 is connected to the first pole of the first capacitor C1, and the second pole thereof is connected to the first trigger signal terminal STU;

[0043] The gate of the second transistor T2 is connected to the first clock signal terminal CLK1, its first pole is connected to the low-level terminal VGL, and its second pole is connected to the first pole of the first capacitor C1;

[0044] The gate of the third transistor T3 is conne...

Embodiment 3

[0071] An embodiment of the present invention provides a shift register, which is characterized in that it includes a multi-stage shift register unit as described in the above embodiment, and the shift register unit in the shift register is the same as the shift register unit in the above embodiment. The bit register unit has the same advantages, which will not be repeated here.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com