Method for performing calibration time delay error testing on time delay calibration switch of intelligent substation

A smart substation and time delay error technology, applied in the direction of data exchange network, electrical components, digital transmission system, etc., can solve the problems such as the inability to measure the delay calibration error of the time delay calibration switch, so as to reduce the knowledge level requirements, test The effect of high efficiency and simple parameter setting process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In the following, the method for testing the delay error of the smart substation delay calibration switch provided by the present invention will be described in detail in conjunction with the accompanying drawings and specific embodiments.

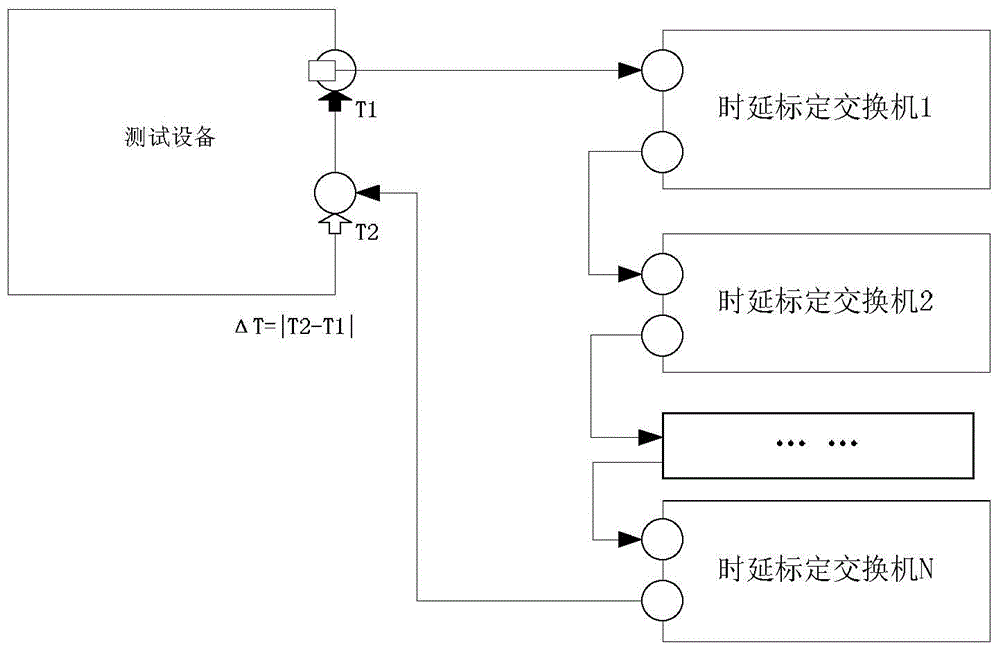

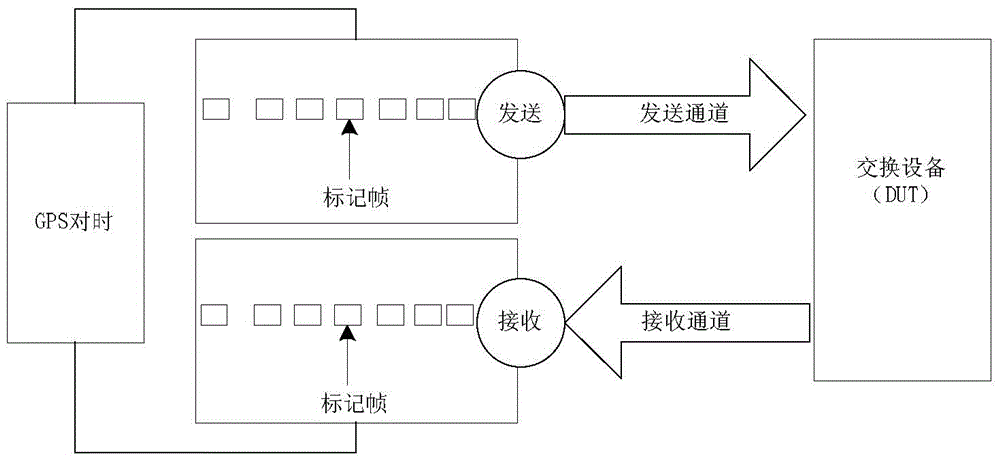

[0029] The method for testing the delay error of the intelligent substation delay calibration switch provided by the present invention adopts the "delay calibration switch" to carry out IEC61850-9-2 sampling value (SV) networking, and the protection device does not depend on the external synchronous clock source. The interpolation method realizes SV synchronization, which solves the problems of large number of optical fibers in smart substations and difficult maintenance of the secondary system under the current SV "direct mining" mode. Delay Calibration The switch calibrates the delay value of switch transmission and processing SV message in the specific field of each frame of SV message. For cascading of multiple switches, this val...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com