Multi-level collaborative and shared storage device and memory access method in gpdsp

A shared storage, multi-level technology, applied in memory systems, instruments, electrical digital data processing, etc., can solve problems such as difficulty in peak computing performance, different data access delays, long memory access delays, etc., to meet high-speed real-time data signals Processing, improving computing efficiency, and realizing the effect of data transmission delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with the accompanying drawings and specific preferred embodiments, but the protection scope of the present invention is not limited thereby.

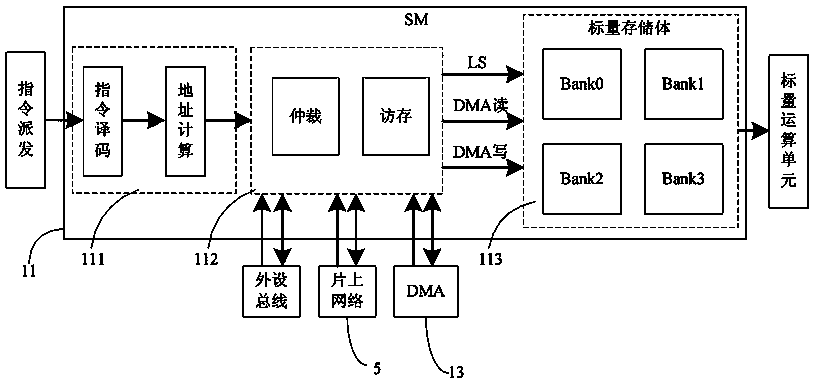

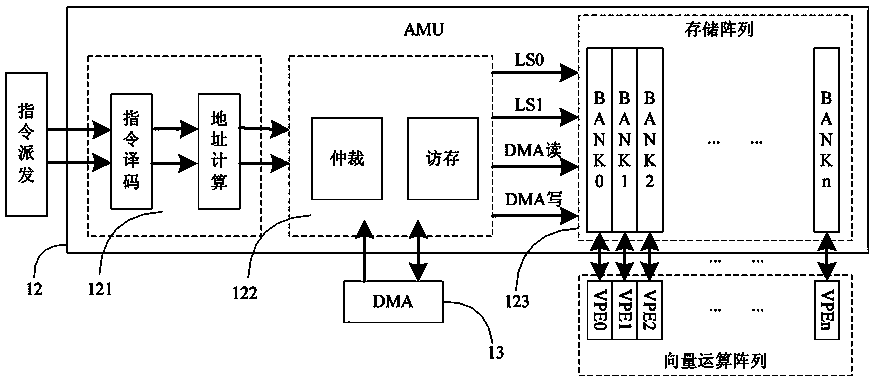

[0043] Such as figure 1 As shown, the multi-level collaborative and shared storage device in the GPDSP of this embodiment includes a plurality of DSP cores 1 and a global shared cache unit 2 (GSC) for caching off-chip storage data, and each DSP core 1 passes through the network on chip 4 respectively. Connect the global shared cache unit 2; each DSP core 1 includes a parallel scalar storage unit 11 (SMU) and a vector array storage unit 12 (AMU), and each DSP core 1 passes through its own scalar storage unit 11 and vector array storage unit 12 In-core data access is performed, and data is shared through the global shared cache unit 2.

[0044] In this embodiment, aiming at the characteristics of the application requirements of GPDSP, each DSP core 1, the scalar ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com