Anti-interference method of synchronous clock device of intelligent substation

A technology for smart substations and synchronous clocks, applied in synchronous devices, electrical components, digital transmission systems, etc., to achieve the effects of improving transmission efficiency, maintaining timing accuracy and stable operation, and avoiding abnormalities or even interruptions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0019] An anti-jamming embodiment of the present invention includes the following steps:

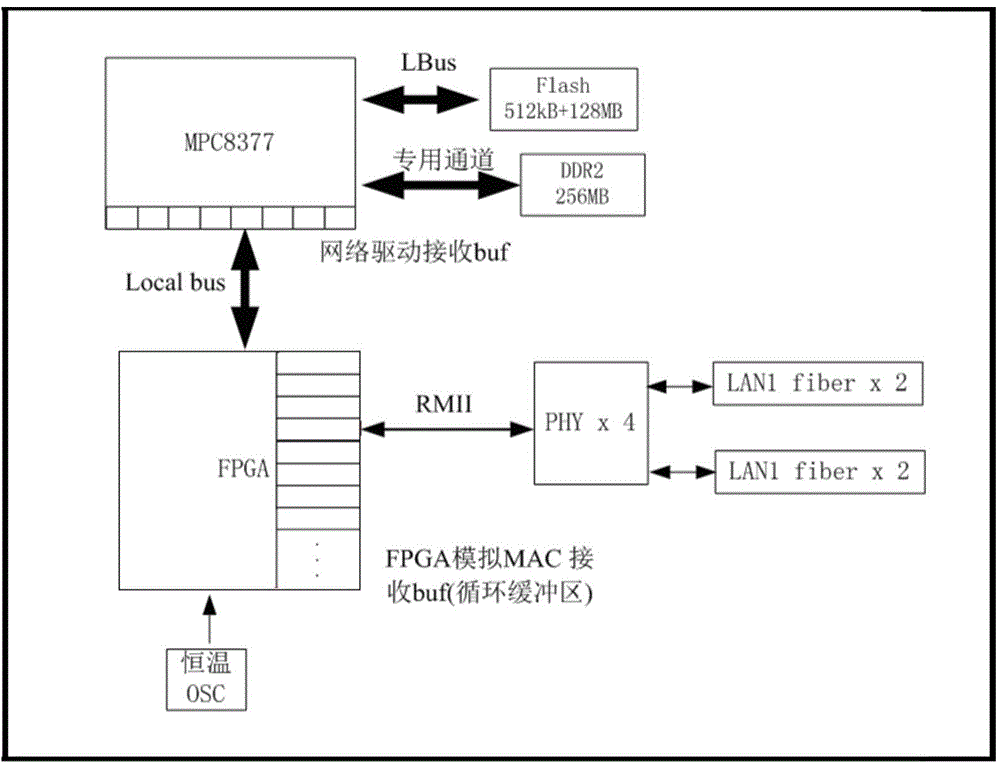

[0020] 1) Device FPGA simulates MAC to receive network messages, and establishes a circular buffer, the number of which is set to A.

[0021] 2) The FPGA counts the number of messages with the same CRC, and judges whether the number of messages exceeds the preset threshold within a preset time interval. If the number of messages exceeds the preset threshold, the message is a storm message; Block the message for a period of time, and restart the detection after the blocking timeout.

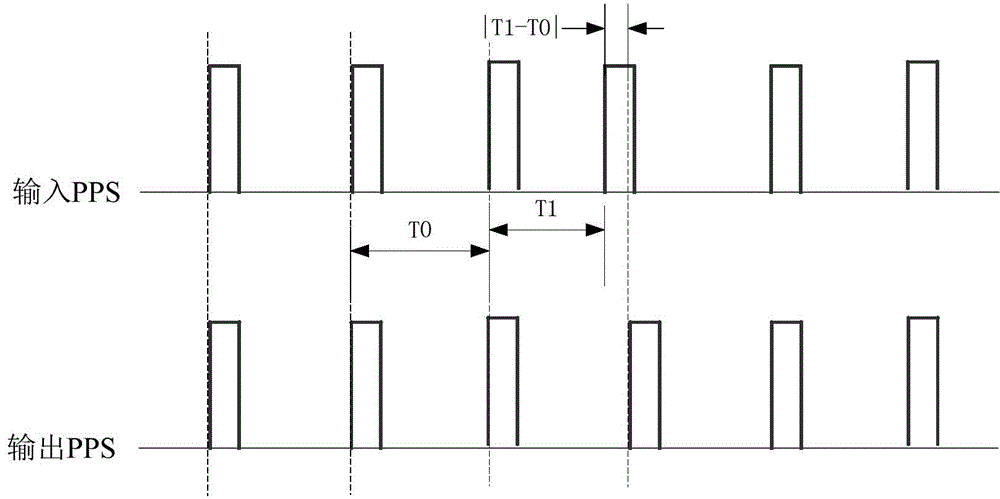

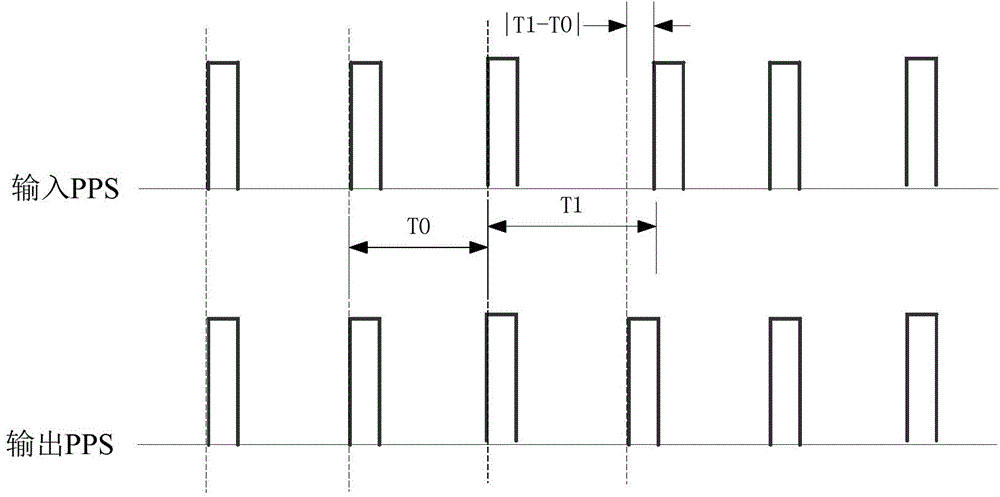

[0022] 3) For PTP time synchronization, FPGA simulates MAC to shield the broadcast, and only receives PTP messages with fixed Ethernet type and fixed UDP port number. The synchronous clocks currently used in smart substations are all based on 802.3 PTP time synchronization. Only receive ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com