Method and device for eliminating clock jitter in analog-to-digital conversion and digital predistortion method

A technology of clock jitter and analog-to-digital conversion, applied in the direction of physical parameter compensation/prevention, improving amplifiers to reduce nonlinear distortion, etc., can solve the problem of deteriorating digital signal signal-to-noise ratio, affecting digital pre-distortion performance, and not considering the impact of clock jitter etc. to achieve the effect of improving linearization performance, eliminating clock jitter, and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] All features disclosed in this specification, or steps in all methods or processes disclosed, may be combined in any manner, except for mutually exclusive features and / or steps.

[0048] Any feature disclosed in this specification, unless specifically stated, can be replaced by other equivalent or similar purpose alternative features. That is, unless expressly stated otherwise, each feature is one example only of a series of equivalent or similar features.

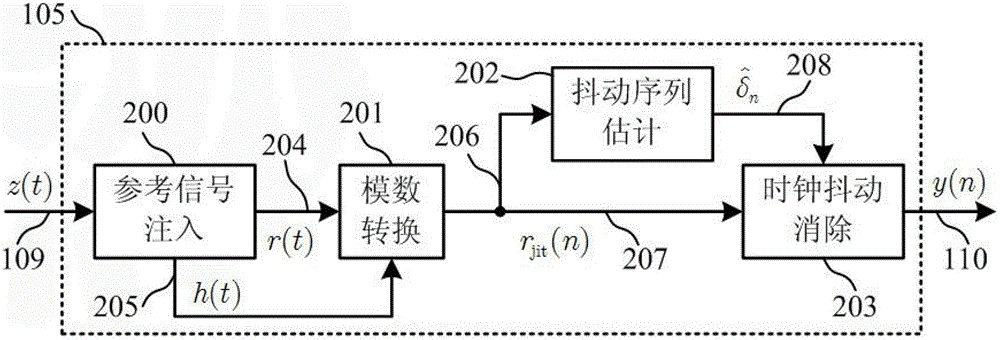

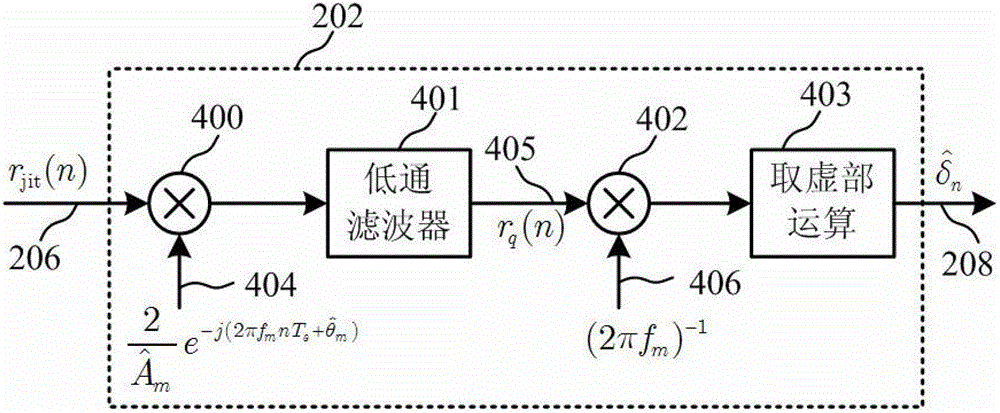

[0049] Such as figure 1 , figure 2 , an embodiment of the method for eliminating clock jitter in the analog-to-digital conversion process includes:

[0050] Step 1: Receive an analog signal z(t) 109 .

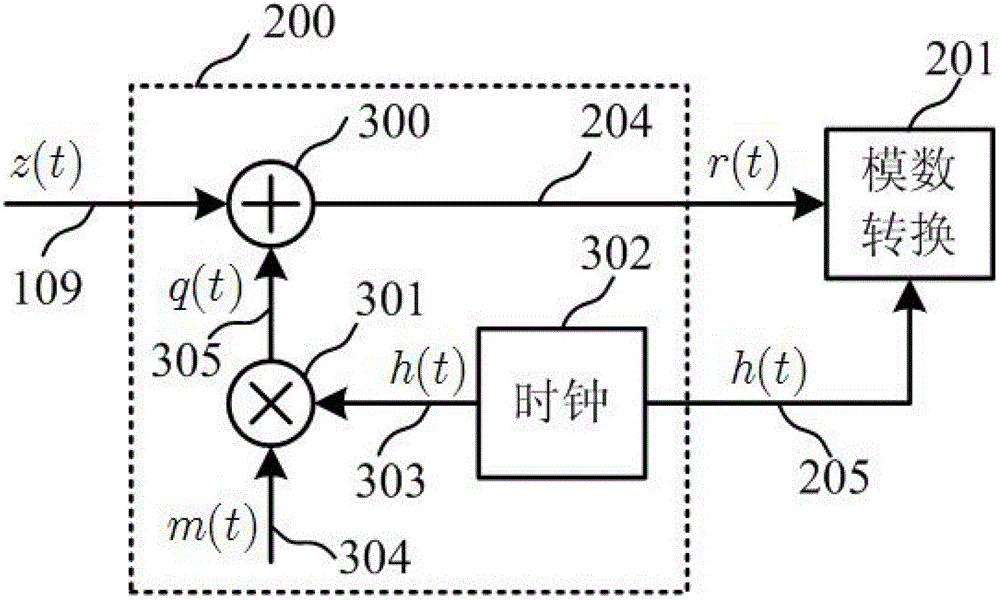

[0051] Step 2: Provide clock signal h(t)205 to the analog-to-digital conversion module, h(t)=cos(2πf s t+β(t)), f s Represents the clock frequency of the selected crystal oscillator (this value is a known value), and β(t) represents the phase noise. At the same time, the product of the clock signal h(t) 303 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com