Fault detection method of analog circuit

A technology for analog circuit and fault detection, applied in analog circuit testing, electronic circuit testing, etc., can solve the problems of long test time, inability to fully meet the actual needs of the project, and insufficient test information

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

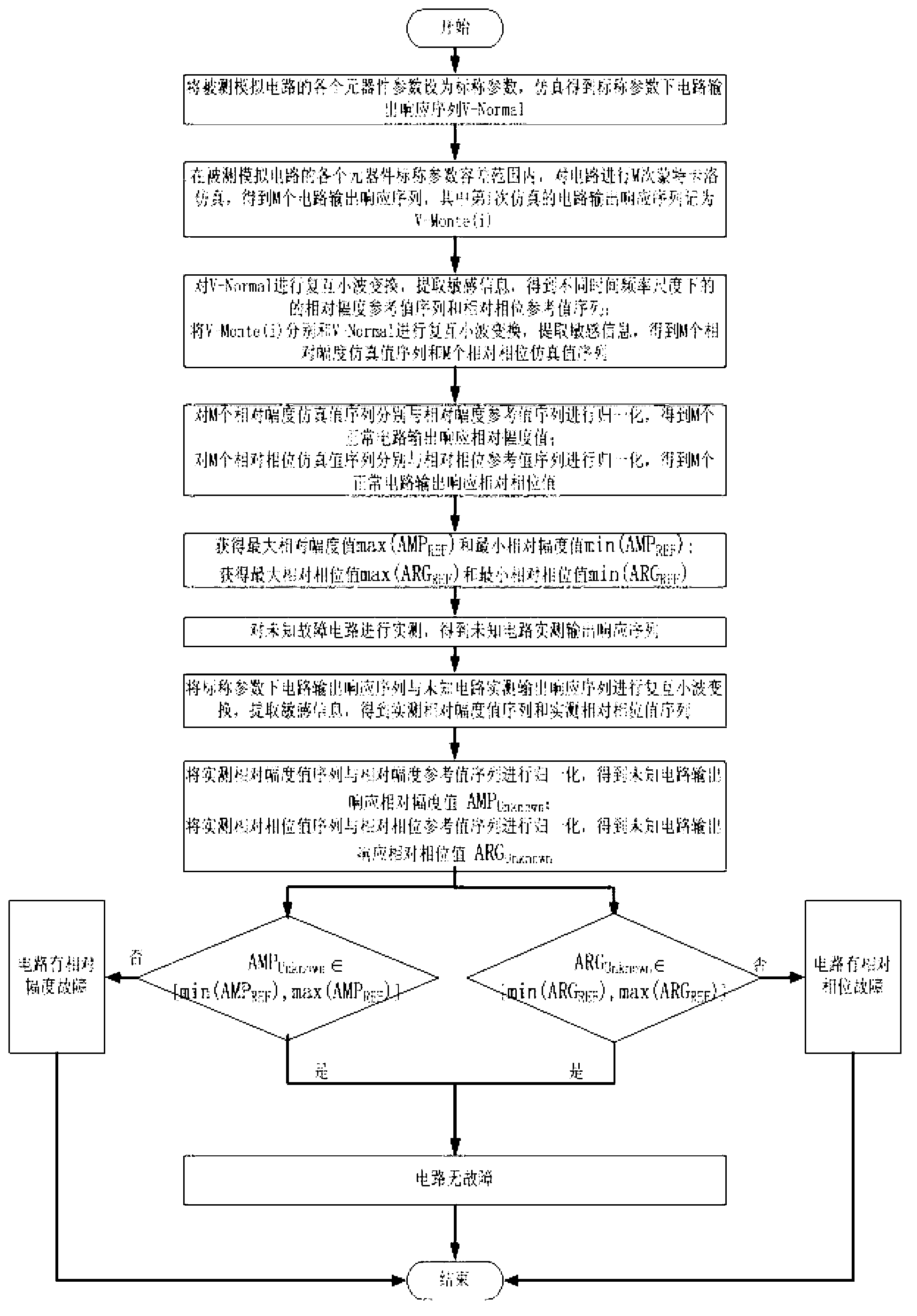

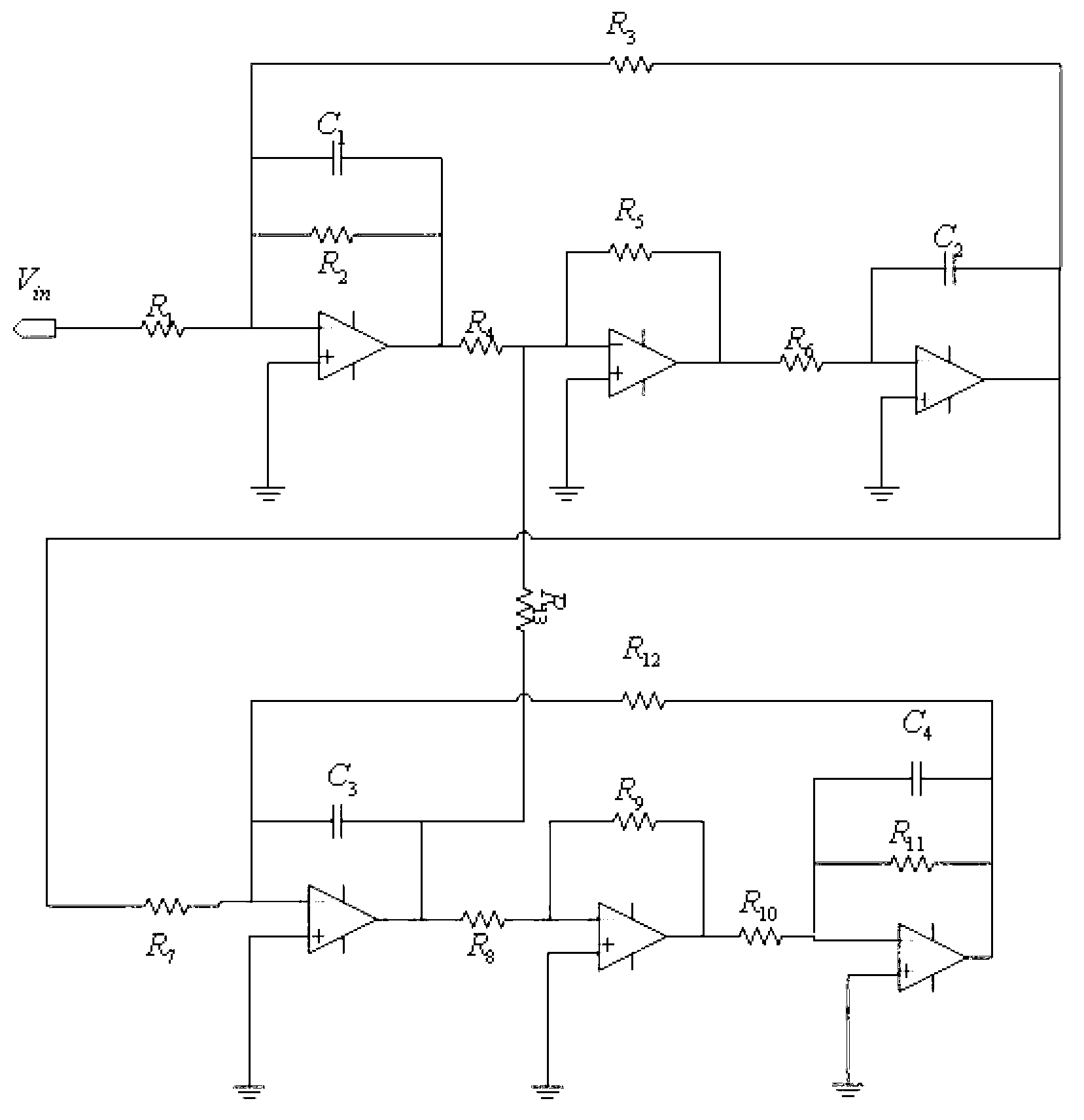

[0063] Such as figure 1 , figure 2 , image 3 shown. The international benchmark jumping frog circuit is selected to verify the analog circuit fault detection method of the present invention. The fault detection method steps of the analog circuit are as follows:

[0064] (1) Set the parameters of each component of the analog circuit under test as nominal parameters, that is, figure 2 R in 1 ~R 13 =10KΩ, C 1 =C 4 =10nF, C 2 =C 3 =20nF, image 3 C in 1 =6pF. The tested analog circuit is simulated in HSPICE, the input VIN is a 1kHz sine wave with an amplitude of 3V, the output VOUT is sampled at 100K sps, and 2048 points are stored each time to obtain the circuit output response sequence under the nominal parameters.

[0065] (2) Within the tolerance range of the nominal parameters of each component of the analog circuit under test, conduct 2000 Monte Carlo simulations on the analog circuit under test to obtain 2000 circuit output response sequences.

[0066] (3) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com