Method and device for optimizing mistake correcting mechanism

A mechanism and error technology, applied in the field of optimizing error correction mechanism, can solve the problems of unfavorable competition, large chip area and high cost, and achieve the effect of improving market competitiveness, optimizing working mode, and reducing the number of logic gates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

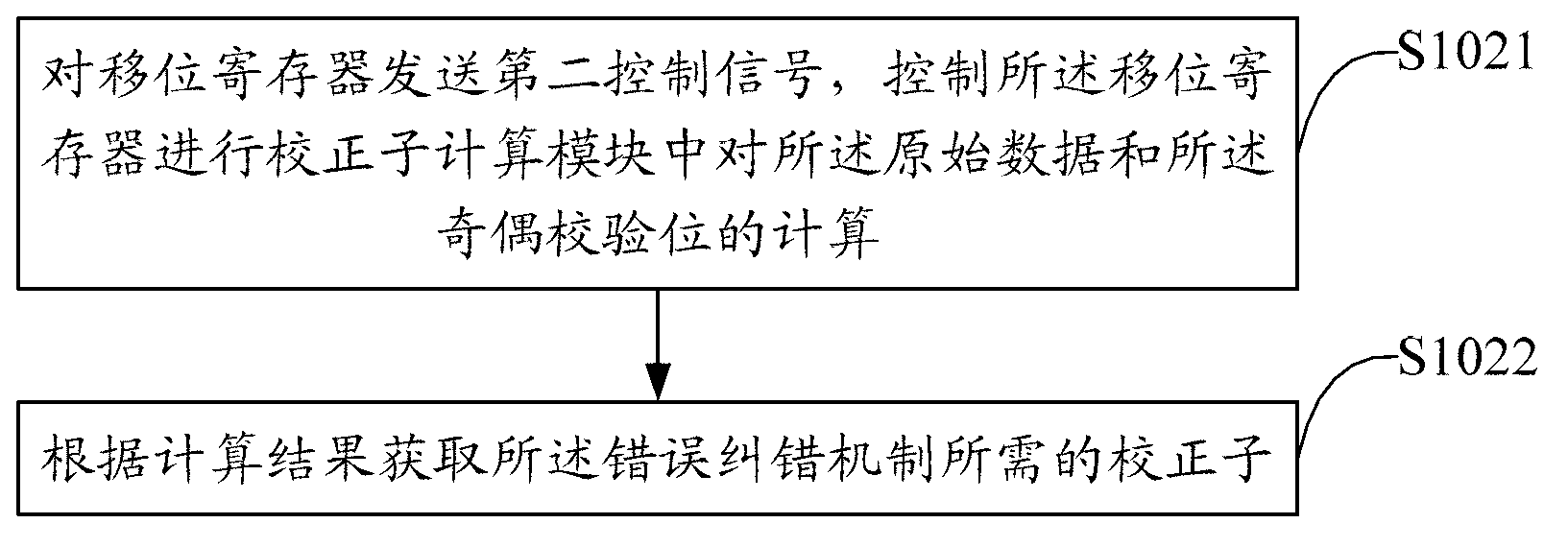

[0032] The solution of the embodiment of the present invention is mainly to optimize the working mode of the error correction mechanism by allowing the encoding module and the syndrome calculation module in the error correction mechanism to share the same shift register according to different control signals, which not only ensures The error correction performance of the error correction mechanism is improved, and the number of logic gates of the error correction mechanism can be reduced.

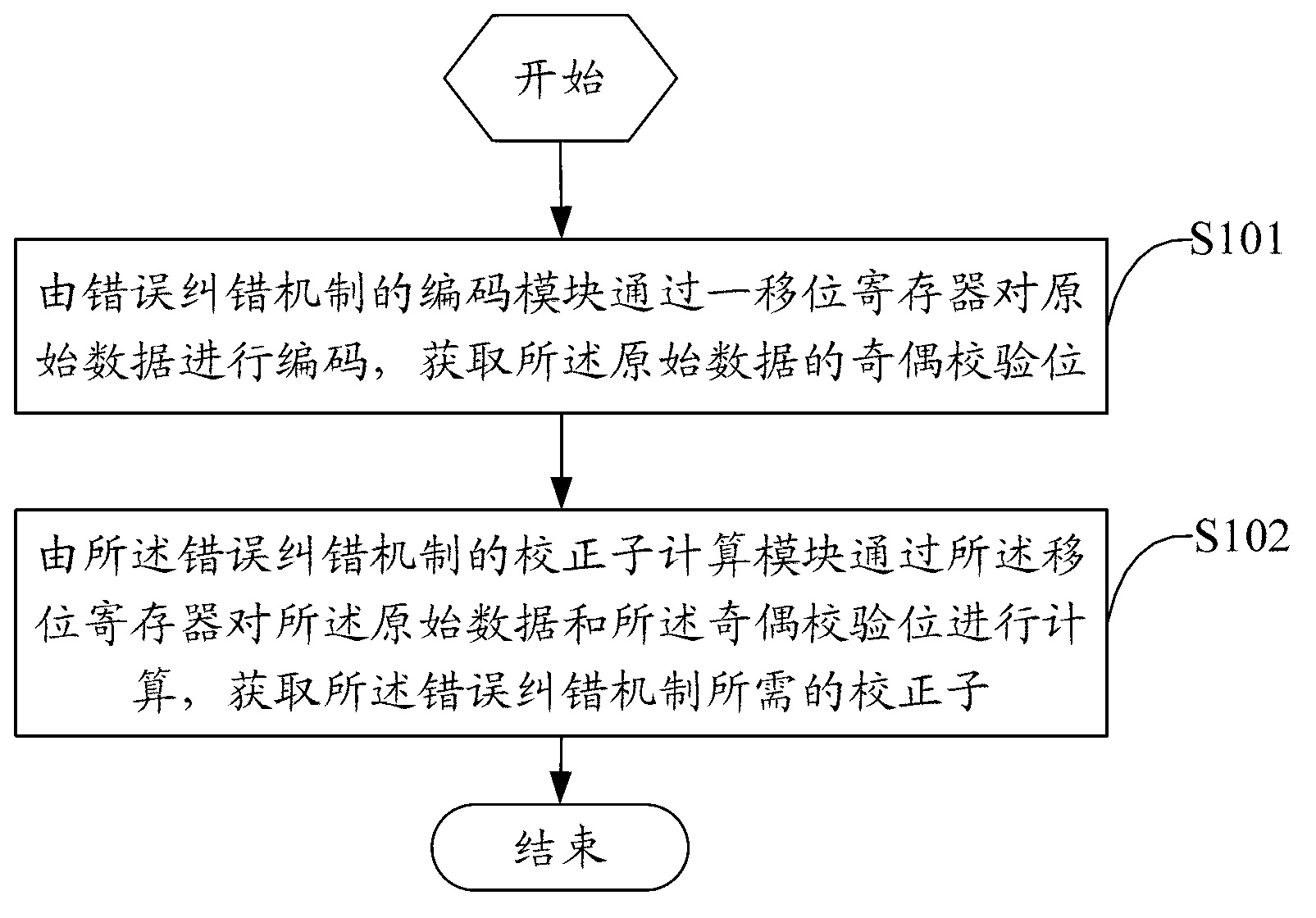

[0033] Such as figure 1 As shown, a preferred embodiment of the present invention proposes a method for optimizing the error correction mechanism, including:

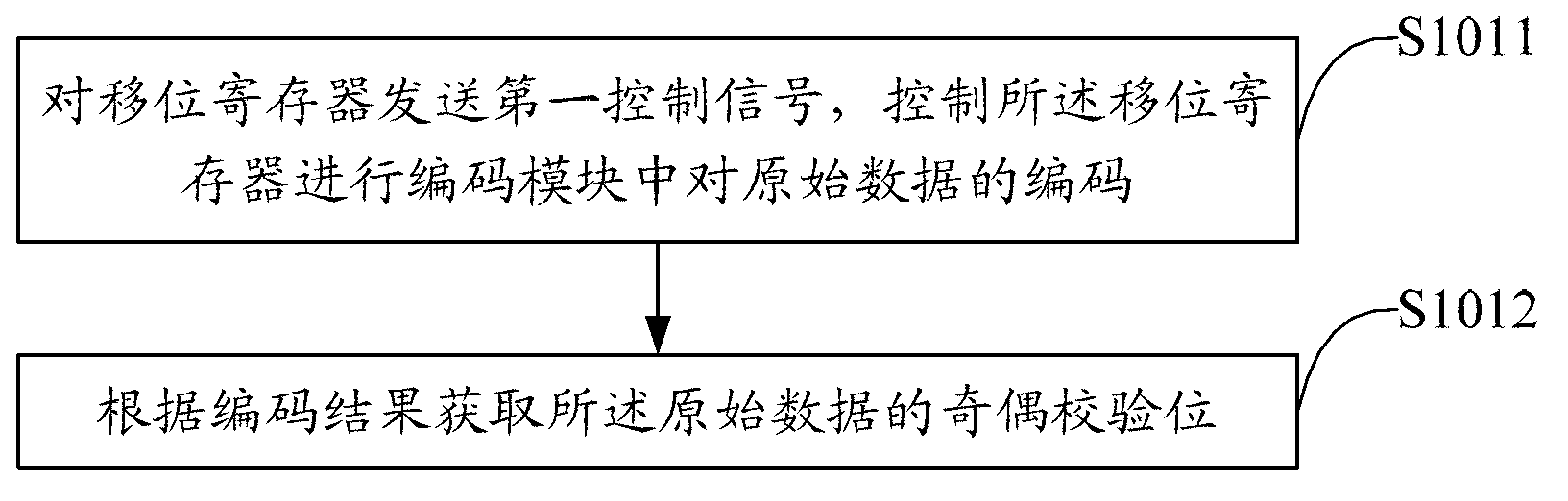

[0034] Step S101, the encoding module of the error correction mechanism encodes the original data through a shift register, and obtains the parity bit of the original data;

[0035] Assuming that the maximum error correction capability of the error correction mechanism is 30 bits, and under the Galois Field 13 domain, when the origi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com