A U-type channel tunneling transistor with stacked structure and its preparation method

A technology of tunneling transistors and stacked structures, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of small device turn-on current, low tunneling efficiency, and large energy band spacing, so as to improve energy efficiency. The effect of belt bending, reducing the tunneling length, and increasing the turn-on current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

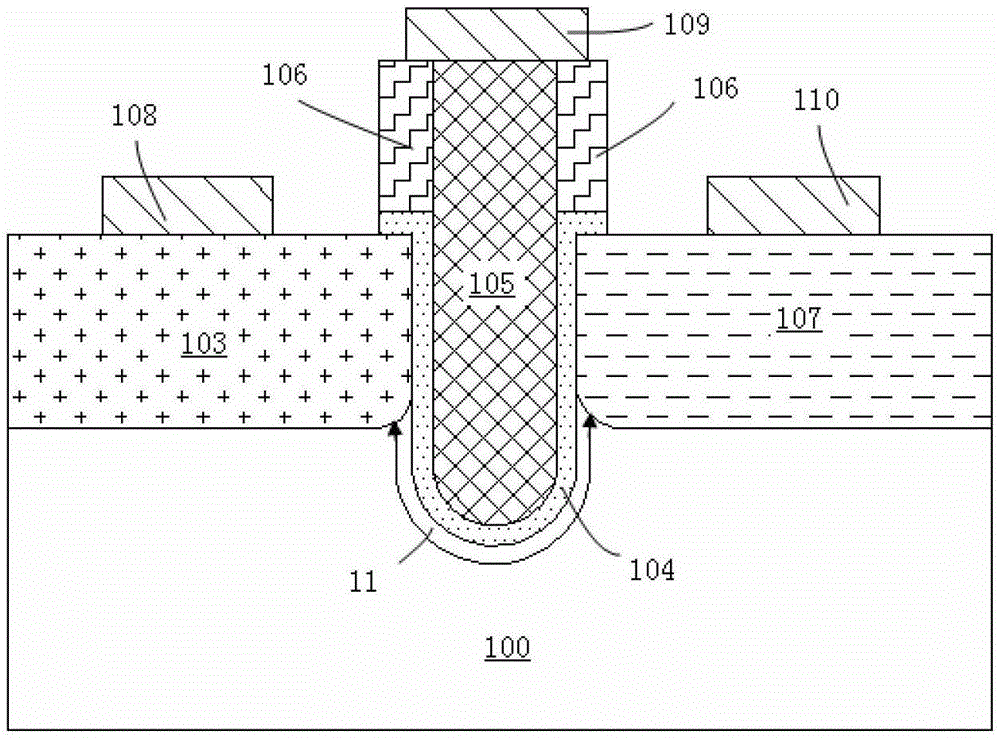

[0033] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. In the drawings, for the convenience of illustration, the thicknesses of layers and regions are enlarged or reduced, and the sizes shown do not represent actual sizes. Although these figures do not fully reflect the actual size of the device, they still completely reflect the mutual positions between the regions and the constituent structures, especially the upper-lower and adjacent relationships between the constituent structures.

[0034] figure 2 It is an embodiment of the U-shaped channel tunneling transistor with stacked structure disclosed by the present invention, and it is a cross-sectional view along the channel length direction of the device. Such as figure 2 , the semiconductor substrate 200 with the first doping type can be single crystal silicon, polycrystalline silicon or silicon-on-insulator, and is doped with a low co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com