Insulated gate bipolar transistor device structure and fabrication method thereof

A technology of bipolar transistors and device structures, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as large turn-off loss and long device turn-off time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

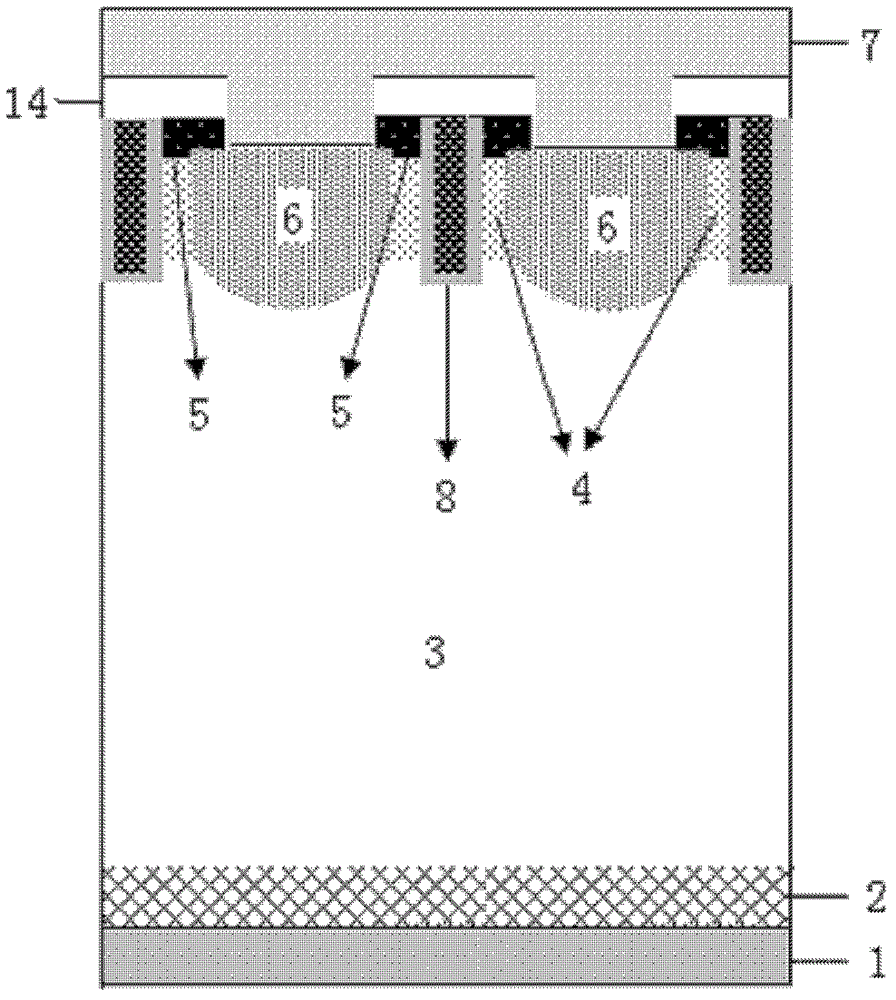

[0024] Embodiment one, see Figure 3-5 shown.

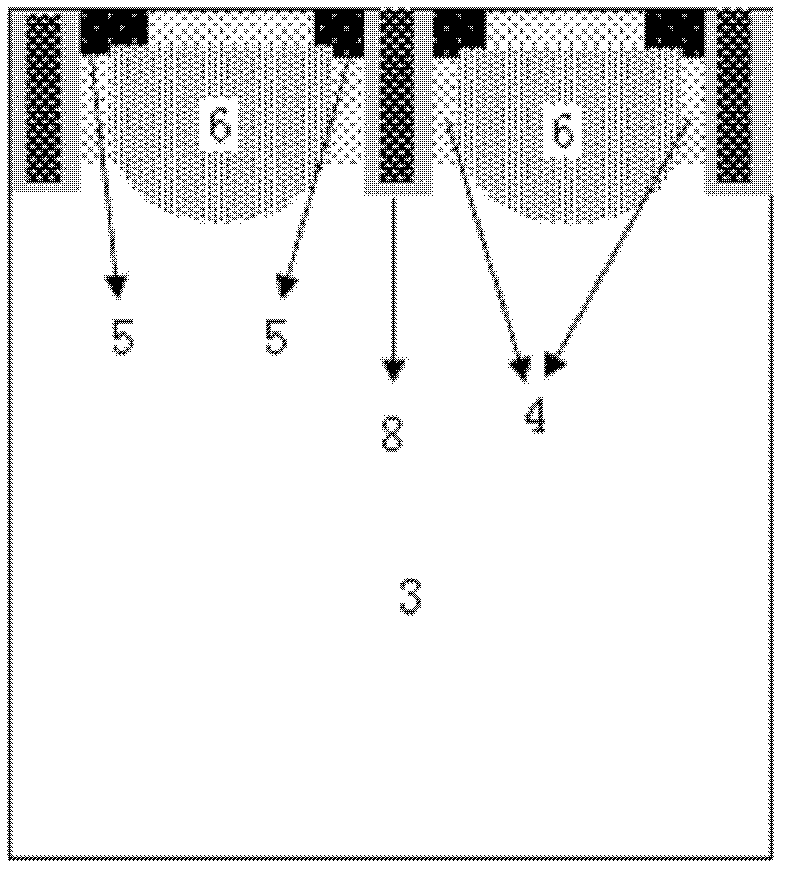

[0025] Step 1. Combine image 3 As shown, an N-type voltage-resistant body region 3 is formed, and a P body region 6 , a channel region 4 , a trench 8 and an N+ emitter region 5 are respectively formed on the upper end of the N-type voltage-resistant body region 3 . That is to complete the manufacturing process of the main structure on the front of the device, which can be completed by using various existing manufacturing process methods.

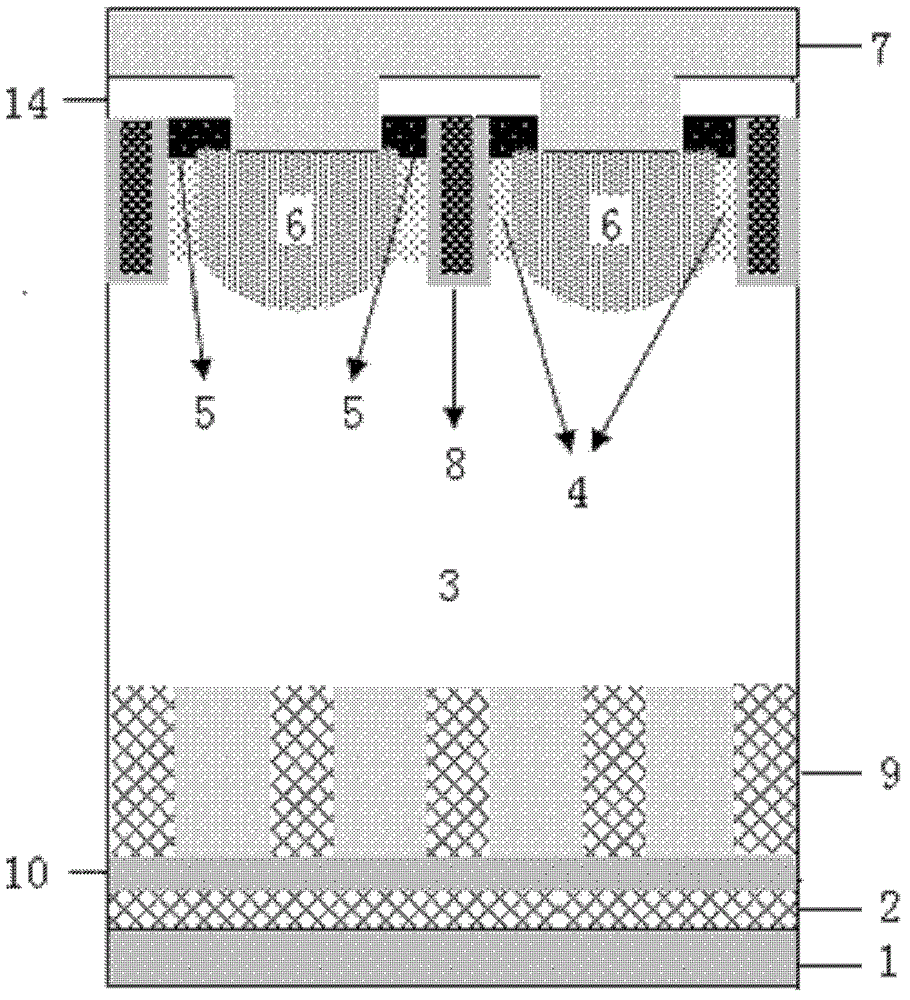

[0026] Step two, combine Figure 4 As shown, a plurality of deep trenches are etched at the lower end of the N-type voltage-resistant body region, and a super junction structure region 9 is formed by using an existing super junction structure manufacturing method. For example, the super junction structure region 9 composed of alternately arranged N-type semiconductors and P-type semiconductors is formed by filling the trenches with epitaxial growth.

[0027] Step three, combine Figure 5 ...

Embodiment 2

[0030] Embodiment two, combining Figure 6-8 shown.

[0031] Step 1. Combine Figure 6 As shown, the super junction structure region 9 is formed on the upper end of the higher concentration N-type substrate 11 .

[0032] Step 2. Combine Figure 7 As shown, an N-type voltage-resistant body region 3 with a lower concentration and a certain thickness is epitaxially grown on the upper end of the super junction structure region 9 . The thickness of the N-type withstand voltage body region 3 is determined by the withstand voltage level of the device.

[0033] Step 3. Combine Figure 8 As shown, the front structure of the device is formed on the upper end of the N-type voltage-resistant body region (the front side of the device), that is, the P body region 6, the channel region 4, the trench 8, the N+ emitter region 8 and the isolation dielectric layer 14 are formed respectively; After metallization, the emitter 7 is formed.

[0034] Step 4. Combine figure 2 , 8 As shown, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com