Conductive plug and method for forming same

A conductive plug and semiconductor technology, applied in circuits, electrical components, electrical solid devices, etc., can solve problems such as inability to control MOS transistors, achieve improved device performance, easy control of etching time, and reduce process steps.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The method for forming the multi-gate field effect transistor in the prior art specifically includes:

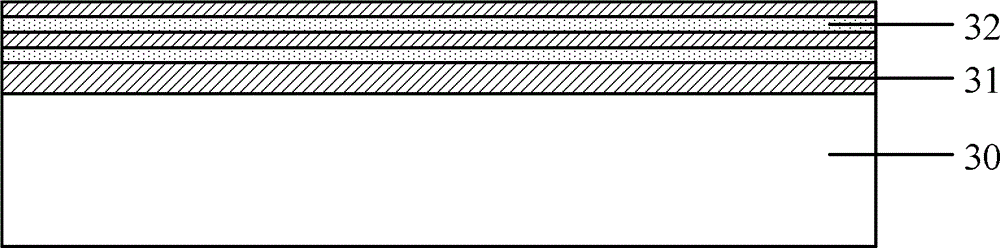

[0054] Please refer to figure 2 , providing a semiconductor substrate 30, on which silicon germanium layers 31 and silicon layers 32 are alternately formed, and impurity ions are doped in the silicon layers 32;

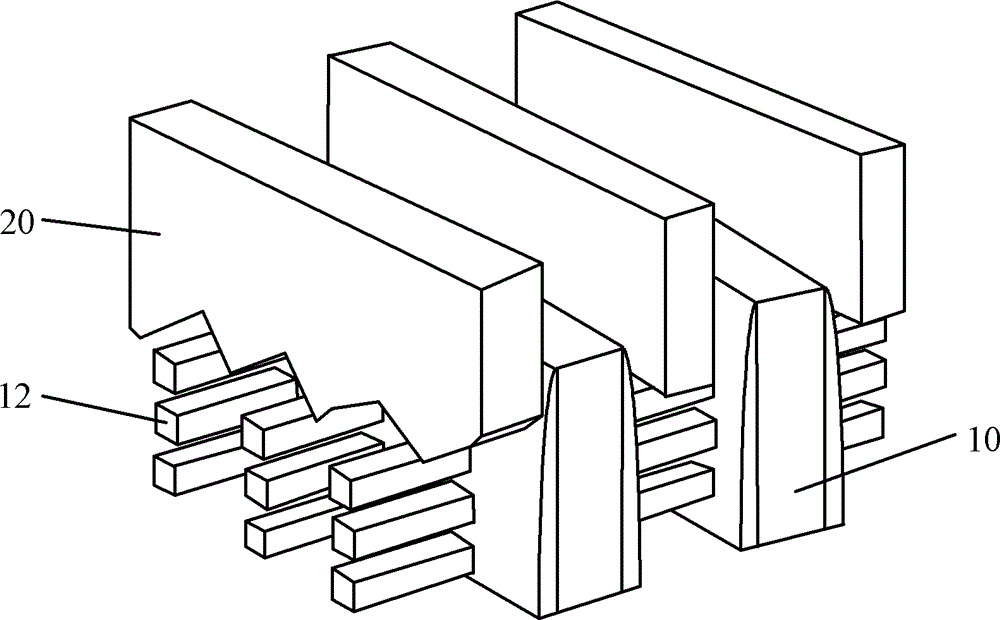

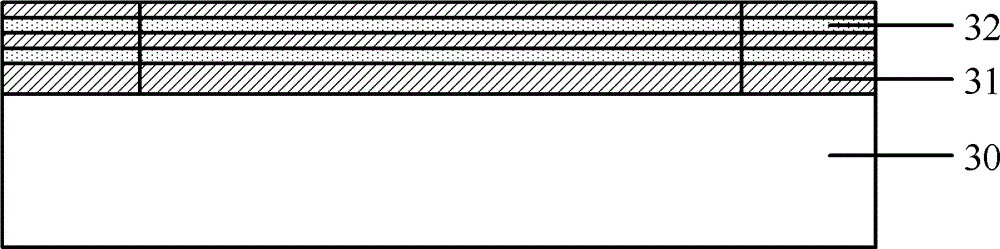

[0055] Please refer to image 3 with 4 , the Figure 4 for image 3 A schematic diagram of the three-dimensional structure, etching the silicon germanium layer 31 and the silicon layer 32 in some areas to form a fin-shaped stacked structure of the silicon germanium layer 31 and the silicon layer 32;

[0056] Please refer to Figure 5 , the silicon germanium layer 31 is wet-etched to remove the silicon germanium layer 31 in the laminated structure of the fin-shaped silicon germanium layer 31 and the silicon layer 32, and the silicon layer between the silicon germanium layers 31 forms a nanometer A wire active region 33, forming a gate dielectric layer (...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com