FPGA (field programmable gata array)-based clock data recovery processing method

A technology of clock data recovery and processing method, which is applied in the direction of digital transmission system, automatic power control, electrical components, etc. It can solve the problem that clock data recovery chips are difficult to meet high-speed clock frequency and fast recovery at the same time, and it is difficult to apply burst clock data Restoration processing and other issues to achieve the effect of ensuring accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

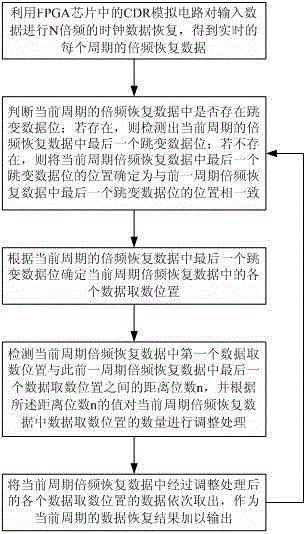

Image

Examples

Embodiment Construction

[0019] The technical solution of the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

[0020] In the existing technology, because only relying on the CDR analog circuit of the FPGA to recover the clock data requires a long recovery phase lock time to ensure the accuracy of the recovery, it cannot meet the requirements for fast recovery of the burst clock data recovery; The clock data recovery realized by the digital oversampling method cannot meet the high-speed clock requirements of the burst clock data recovery due to the limitation of the FPGA digital oversampling frequency; these factors make the clock data recovery based on the FPGA design in the prior art Chips are difficult to apply to burst clock data recovery processing. For this, the present invention proposes a kind of clock data recovery processing method based on FPGA, this method needs to adopt the FPGA chip that is integrated with CDR analog circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com