Method for manufacturing longitudinal power semiconductor device

A technology of power semiconductors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

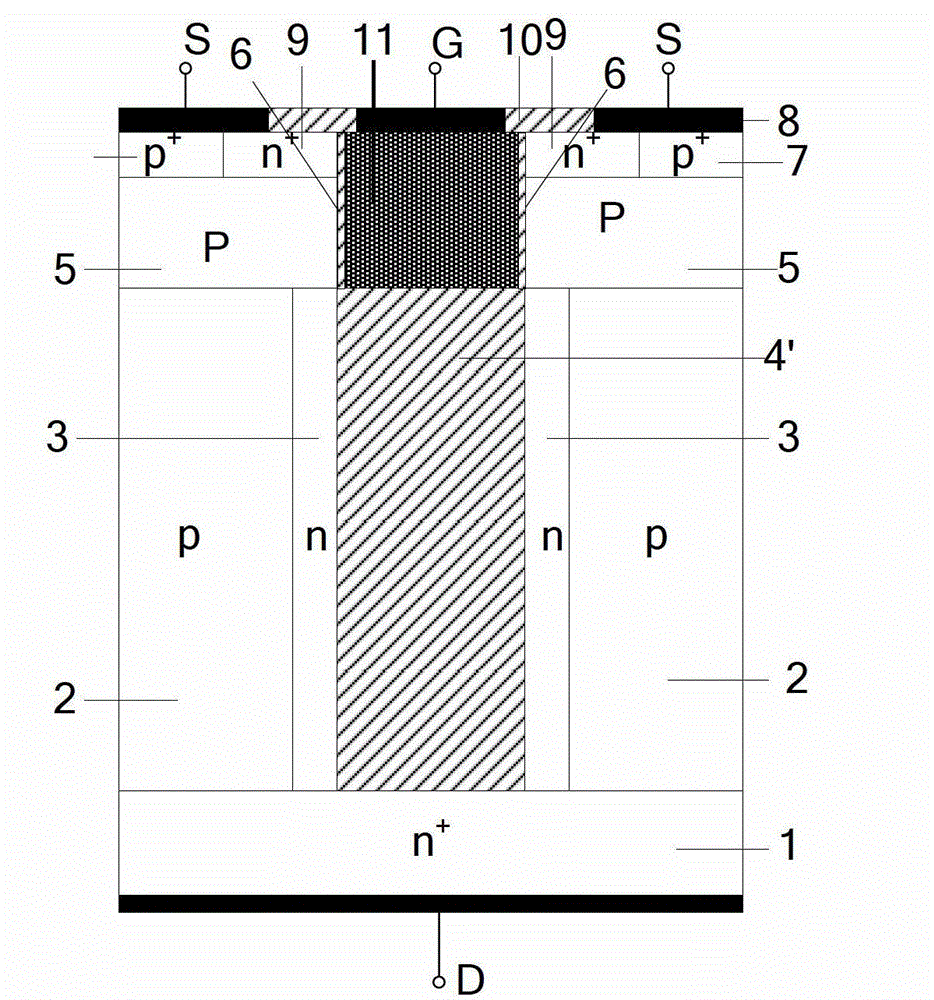

[0065] This example takes the manufacture of N-channel trench gate VDMOS with a dielectric trench as an example to describe in detail the manufacturing method of the vertical power semiconductor device of the present invention. The structural schematic diagram of the N-channel trench gate VDMOS with a dielectric trench is as follows Figure 5 .

[0066] In this example, the method for manufacturing an N-channel trench gate VDMOS with a dielectric trench includes the following specific steps:

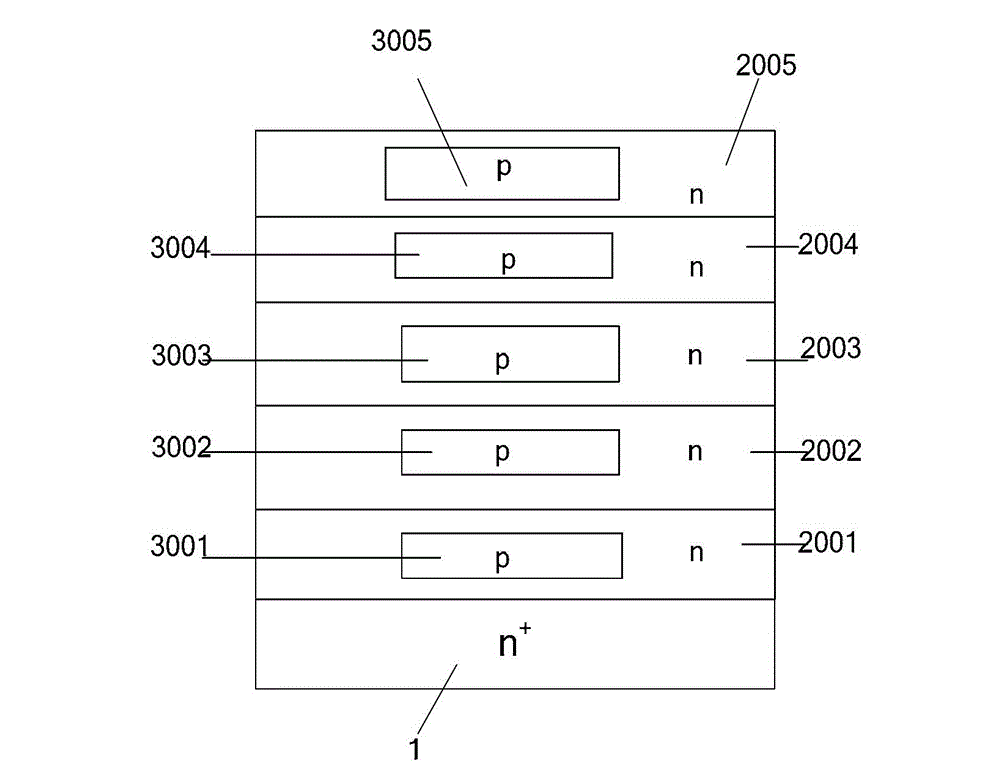

[0067] a. By epitaxial growth, an n-type first semiconductor region 2 is formed on the N+ semiconductor substrate 1, and after the first semiconductor region 2 is formed, it is as follows Figure 6 shown;

[0068] b. Thermally oxidize and grow a thin oxide layer 13 on the top of the first semiconductor region 2, and then deposit Si 3 N 4 Masking layer 14, then coat photoresist 15 again, carry out photoetching, coat photoresist 15 after being coated with as Figure 7 shown;

[0069] ...

Embodiment 2

[0085] This example takes the manufacture of IGBT devices as an example, and its structure diagram is as follows Figure 20 shown.

[0086] The manufacturing process of the semiconductor device of the present invention described in detail in Embodiment 1 is preferably applied to MOS-controlled vertical devices, so as to alleviate the contradictory relationship among withstand voltage, on-resistance and switching loss. And applied in such as Figure 20 In the shown IGBT device, the conductivity type of the semiconductor substrate 1 is opposite to that of the second semiconductor region 3. For the n-channel IGBT, the difference from Example 1 is that the initial material of the semiconductor substrate 1 is P + The conductivity type of the semiconductor substrate 101 is opposite to that of the second semiconductor region 3 , and the rest of the steps are exactly the same as those of the first embodiment.

Embodiment 3

[0088] This example takes the manufacture of P-channel trench-gate VDMOS devices as an example, and its structure diagram is as follows Figure 21 shown.

[0089] The manufacturing process of the semiconductor device of the present invention described in detail in Embodiment 1 can be applied to control vertical devices of N-channel MOS, and can also be applied to control vertical devices of P-channel MOS. Such as Figure 21 As shown, the doping type of the semiconductor substrate 1, the second semiconductor region 3 formed by oblique ion implantation, the body region 5, the body contact region 7, the source region 9 and the corresponding region of the N-channel VDMOS described in Embodiment 1 Just the opposite.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com