Fault detection and reduction in logic circuit

A logic circuit, fault technology, applied in the field of designing high-integrity logic circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

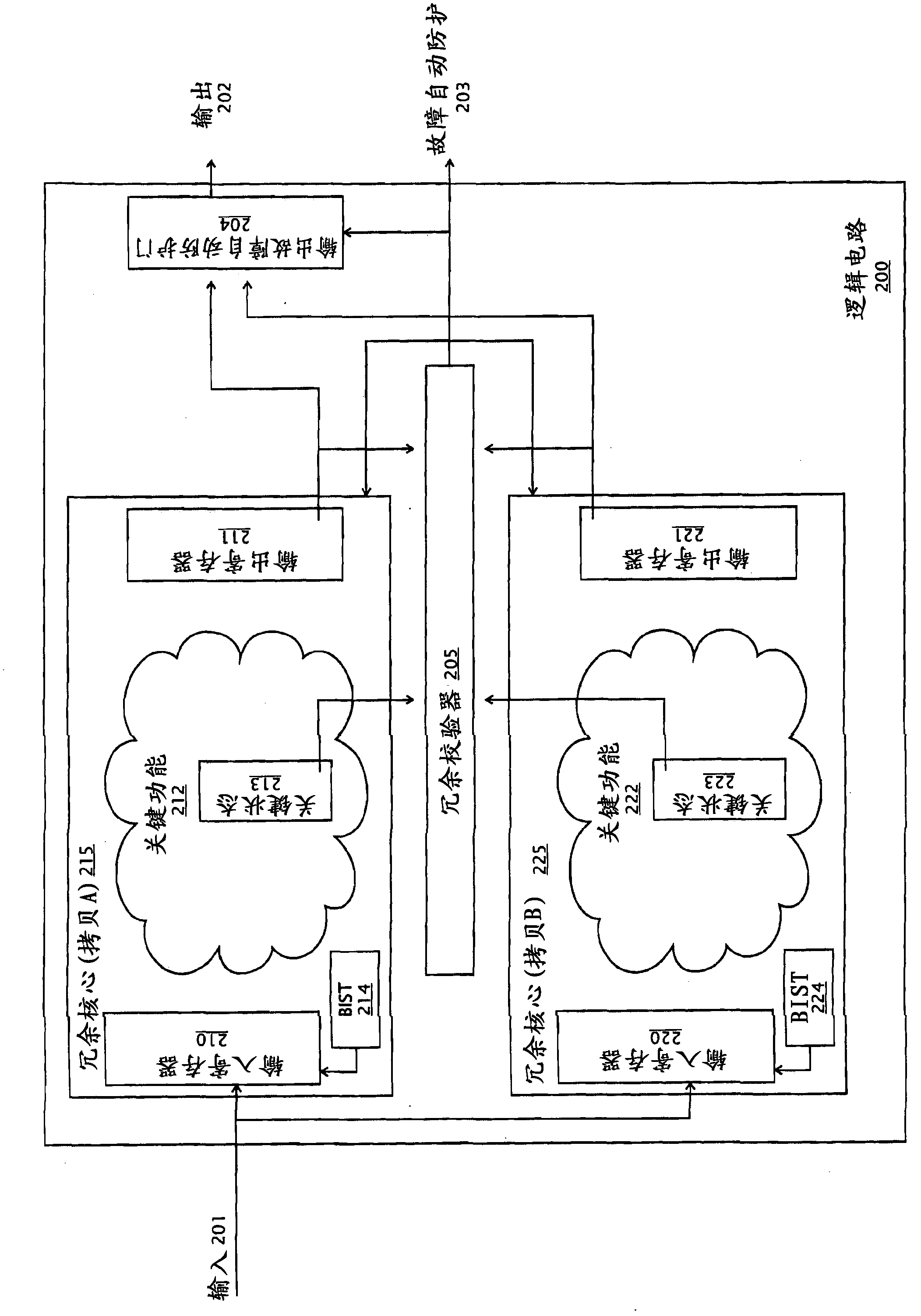

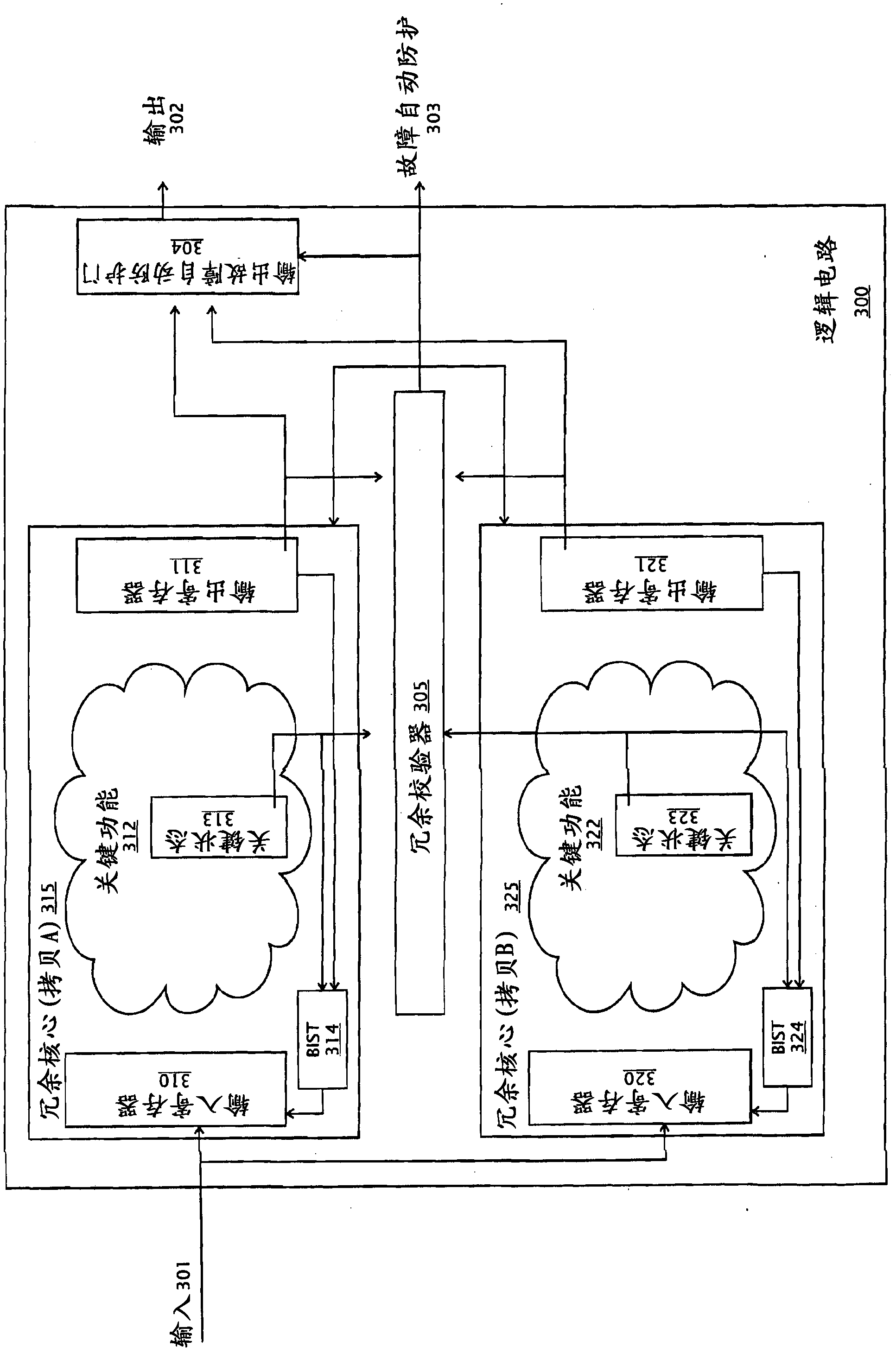

[0025] The main object of the present invention is to provide a highly reliable logic circuit which is guaranteed to perform the intended task when invoked.

[0026] Another object of the present invention is to provide a method for designing fail-safe logic circuits implemented within a single logic device such as a PAL, CPLD, ASIC, gate array, or FPGA. Alternatively and as such, the logic circuitry is implemented in a combination of multiple logic devices on a single printed circuit board (PCB). Alternatively and as such, they are implemented in combinations of multiple printed circuit boards with one or more logic devices such as PALs, CPLDs, FPGAs, ASICs, or gate arrays.

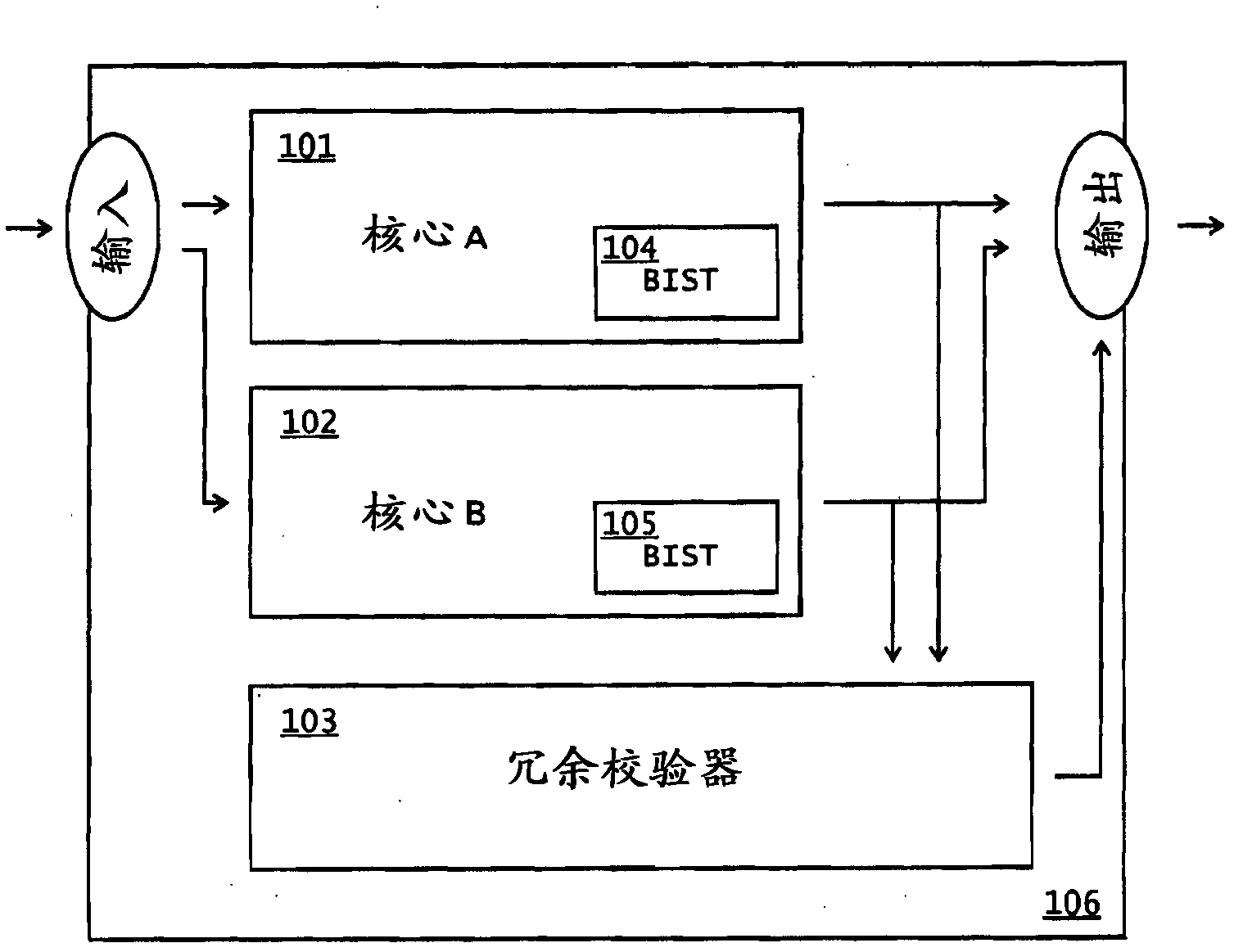

[0027] The present invention can incorporate redundancy and / or fault tolerance at the application level by having multiple parallel systems capable of performing tasks. One approach is to have two or more parallel systems capable of performing tasks. If one of these systems fails and goes into a fail-s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com