Array substrate row driving circuit, display panel and display device

A technology of array substrate rows and driving circuits, applied in static indicators, instruments, etc., to ensure stability and small fluctuations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

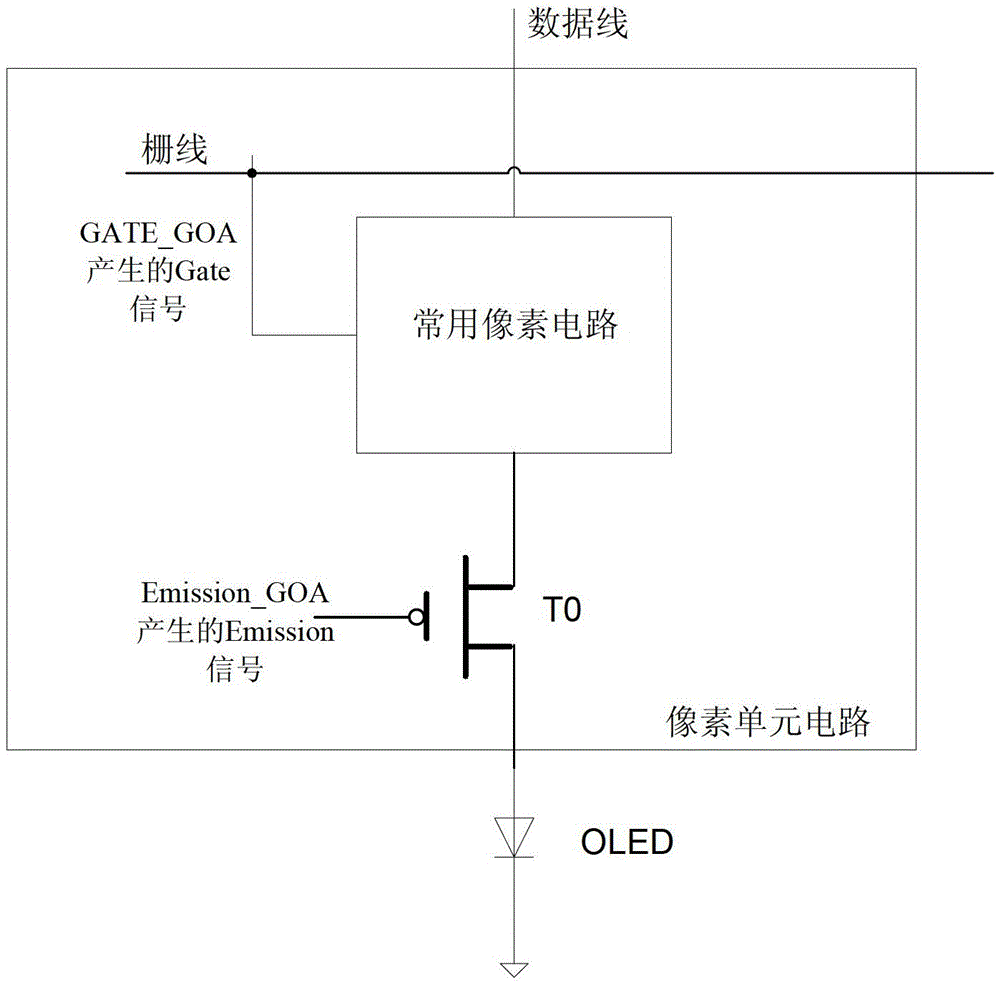

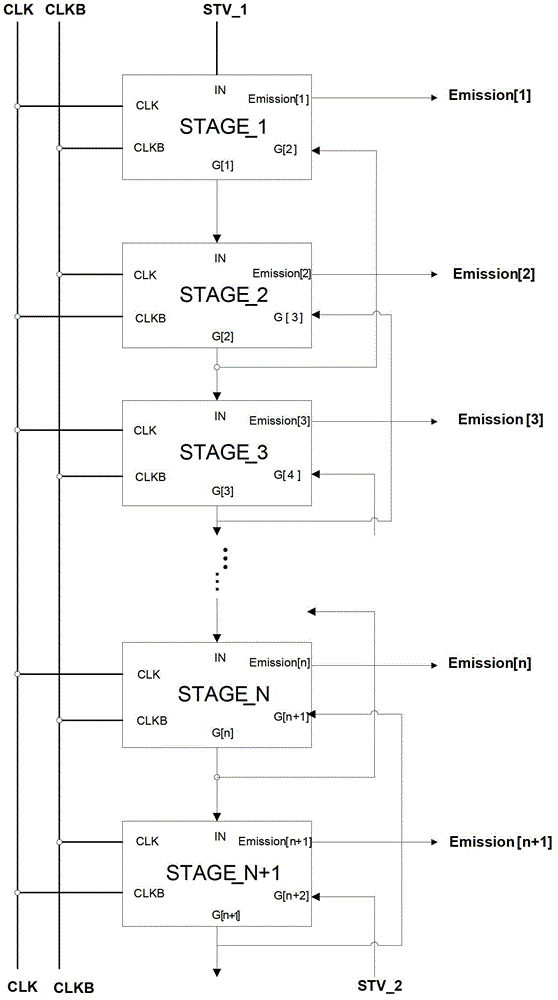

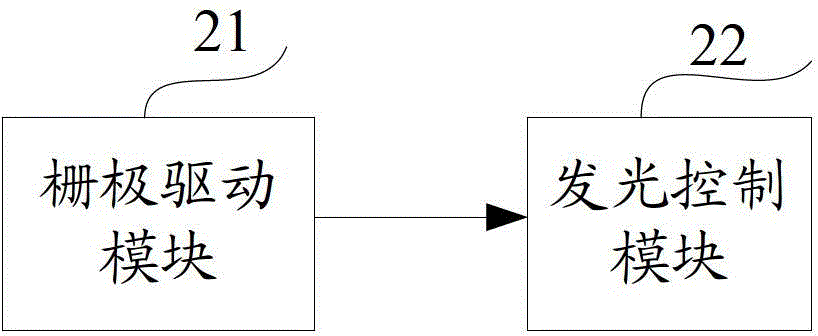

[0041] Embodiment 1 of the present invention provides a row driving circuit for an array substrate, the structure of which is shown in figure 2 As shown, it includes series-connected multi-stage circuit units STAGE_1~STAGE_N+1, and the structure of each stage circuit unit is as follows image 3 As shown, it includes a gate drive module 21 and a light emission control module 22, the gate drive module 21 is used to generate a gate drive signal, the light emission control module 22 and the gate drive signal output of the gate drive module 21 The terminal is connected, and is used to generate a light-emitting control signal for controlling the switch of the organic light-emitting diode under the control of the gate drive signal, and the gate drive signal and the light-emitting control signal are inverted.

Embodiment 2

[0043] Embodiment 2 of the present invention provides a row driving circuit for an array substrate, the structural diagram of which is shown in figure 2 As shown, on the basis of Embodiment 1, the gate drive module 21 includes the first thin film transistor T1 to the seventh thin film transistor T5 and the first bootstrap capacitor C1, wherein,

[0044] The first terminal of T1 is respectively connected to the third terminal of T5 and the second terminal of T4, the second terminal is connected to an external level signal, and the third terminal is connected to the second terminal of C1 and T2 respectively, and serves as the gate drive signal output;

[0045] The first terminal of T3 is connected to the clock signal CLK, the second terminal is respectively connected to the first terminals of T5, C1 and T2, and the third terminal is connected to the gate drive signal output terminal of the upper circuit unit;

[0046] The first terminal of T4 and the second terminal of T5 are ...

Embodiment 3

[0050] Embodiment 3 of the present invention provides a row driving circuit for an array substrate, the structural diagram of which is shown in figure 2 As shown, on the basis of the second embodiment, the gate drive module further includes thin film transistors T6 and T7, wherein the first terminal of T7 is connected to the reverse signal CLKB of the clock signal, and the second terminal is connected to the third terminal of T5 The third terminal is connected to the second terminal of T6 and the first terminal of T1 respectively; the first terminal of T6 is connected to the clock signal CLK, and the third terminal of T6 is connected to the second terminal of T4.

[0051] Transistors T6 and T7 are added to the circuit, which are connected in series with T4 and T5 respectively, so that the working state is more stable, and the connection relationship between the level of point N2 and the high and low levels is further clarified. For example, in the reset period t3, the transist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com